主题中讨论的其他器件: BQ76952EVM

尊敬的团队:

在尝试 使用 BQ769142 PREDISCHARGE 模式功能时遇到问题。

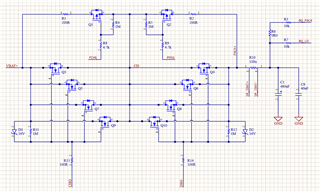

有关电路配置方式的说明。

- 已使用所有保护 FET、其配置 相当于数据表(https://www.ti.com/lit/ds/symlink/bq769142.pdf)的图16

- 主 FET (DSG 和 CHG)每个都是一组4个 N 沟道 FET。

- 预(dis)充电 FET 是具有200R 限流电阻器的 P 沟道 FET。

- 所有栅源上拉电阻均为1 MOhm。

- PACK+上有一个大于200uF 的电容器组、这是我想要的预放电模式。

- PACK+通过10k 上拉电阻器连接到 BQ769142 LD 和 PACK 引脚。

- BQ769142电流检测从未使用过。 SRN 和 SRP 引脚短接在一起。

- 电荷泵电容器为470nF

BQ769142配置为:

- PDSG_EN 位设置为1

- 预放电超时设置为30ms

- 预放电停止增量设置为0 (禁用)

- 电池 UV 阈值为3.0V、电池 OV 阈值为4.2V

- 电荷泵过驱 配置为11V。

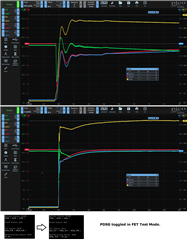

我遇到的问题是 、在测试时(没有发出 ALERT、SS 或 PF 标志) 、我永远无法观察到 PDSG FET 在 DSG FET 之前导通、 尽管看起来很明显、但 在 DSG 开启之前、它应始终开启30ms。 提交 ALL_FETS_ON()命令时,仅打开 CHG 和 DSG。

BAT+设置为22.2V (每节电池3.7V)、PACK+在0V 时断开。

那么,从上面的信息,你能看出任何原因 PDSG 无法工作吗?

可能感兴趣的其他奇数观察结果:

- 在 FET 测试模式下运行时、我可以切换 PDSG FET 、但 出于某种原因、PDSG 和 DSG 都会导通。

- 实际上只要我 运行 CHGTEST ()或 PDSGTEST (), DSG 就会开启。 这是预期结果吗?

- 我无法在不改变信号电平的情况下探测 PCHG 和 PDSG 栅极驱动信号。 当 将 PCHG 或 PDSG 设置为禁用时、 用 DMM 电压探头或10倍示波器探头 pok 这些网络 足以将线路拉低、从而导通 FET。