主题中讨论的其他器件: BQ76940、

问题1:

10块 BQ76952板收集的16个单体电压比正常值低大约10mV。 所有16个通道均低于标准值。

初始化设置错误吗、或者它是其他什么吗?

10mV 稍微大一点、无法通过校准方式进行校正。

问题2:

MCU 读取 MOSFET 的状态。 几乎80%关闭 MOSFET 的可能性..

特别是在 MCU 开关 MOSFET 时, MOSFET 很容易关闭。

还有其他方法可以获取 MOSFET 的状态? 这将不会影响 MOSFET 运行状态、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

问题1:

10块 BQ76952板收集的16个单体电压比正常值低大约10mV。 所有16个通道均低于标准值。

初始化设置错误吗、或者它是其他什么吗?

10mV 稍微大一点、无法通过校准方式进行校正。

问题2:

MCU 读取 MOSFET 的状态。 几乎80%关闭 MOSFET 的可能性..

特别是在 MCU 开关 MOSFET 时, MOSFET 很容易关闭。

还有其他方法可以获取 MOSFET 的状态? 这将不会影响 MOSFET 运行状态、

尊敬的 Wei:

问题1:

如果问题是所有电芯测量中存在一致的偏移、则可能是由于电芯和器件引脚之间放置的电阻器的阻值所致。 您可以尝试按照中概述的步骤进行操作、 第 2.3节:电芯电压偏移校准 共 此应用手册 以查看更改固件中的偏移是否可以解决该问题。

问题2:

我不完全确定"MCU 读取 MOSFET 的状态"是指什么。 关闭 MOSFET 的可能性几乎为80%。" 您是说 MCU 正在读取 MOSFET 的状态并且有时会意外地将其关闭吗?

读取 FET 状态的建议方法是读取 FET 状态寄存器、请参阅 第 12.2.2节:FET 状态寄存器 的 TRM以了解寄存器的说明。 读取该寄存器中的 CHG 和 DSG 位不应影响 FET 的操作。

此致、

马克斯·韦博肯

您好、Max:

感谢您的建议。

当前的问题对我们来说非常关键。 我们花了很多时间讨论这个问题、但却无法解决这个问题。

同时、我们与 BQ76952的其他一些用户讨论过、但我们无法得到满意的答案。 非常感谢您的建议。

问题1:

我们检查了 Cell 输入的输入阻抗、并使用了的参数1KΩ input R、如 BQ76940。 TI 官方评估板是100Ω、根据这条线索应该能够找到问题。 这是偏移较大的原因吗? 您可以在 EVM 板中检查1K 输入 R。

此外、当软件初始化76952时、不会设置第2.3节:电芯电压偏移校准的偏移值。

我们还想知道是否可以校准10mV 的偏移? 似乎10mV 是一个很大的偏移。 在之前的产品中、我们仅校准由电路板元件差异引起的1-2mV 偏移。

问题2:

我们使用低侧 FET 控制、通过 AFE 器件的 DDSG 引脚、DCHG 引脚控制 MOSFET。 现在情况是每次你写 12.5.6 FET 控制寄存器(0x0097) 读取这里的寄存器中的 第12.2.2节:FET 状态寄存器(0x7F)、 将导致 AFE 器件的 DDSG 引脚、DCHG 引脚在读取数据时很可能关闭 MOS 12.2.20:FET 状态寄存器(0x7F) 寄存器值、还显示 DDSG_PIN (Bit5)、DCHG_PIN (bit4)为1、即 DDSG/DCHG 引脚有效。

尊敬的 Wei:

BQ76952EVM 实际上在 VCx 引脚的 RC 滤波器中使用20 Ω 电阻器。 我建议尝试使用该值、而不是1kOhm、因为这可能是失调电压的来源。

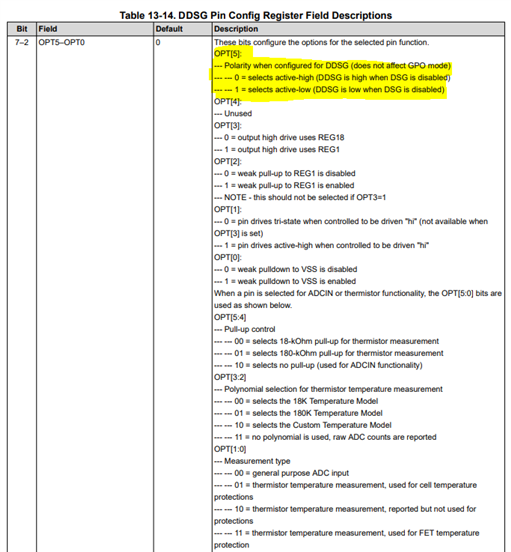

您能检查一下 DDSG 和 DCHG 引脚是设置为高电平有效还是低电平有效、以及这些引脚是您预期的情况吗? 此设置为 设置:配置:DDSG 引脚配置 请参阅下图以了解寄存器映射。

此致、

马克斯·韦博肯

在 BQ76952的初始化期间、我们放入 Settings:Configuration:DCHG Pin Config (0 x9301)、将其初始化为0 xA2、即

OPT[5]= 1、选择低电平有效(禁用 CHG 时 DCHG 为低电平)

opt[2]= 1时、弱上拉至 REG1被启用

PIN_FXN1–PIN_FXN0[0~1]= 2、DCHG

设置:配置:DDSG 引脚配置(0x9302) 也初始化为0xA2 ć、

OPT[5]= 1、选择低电平有效(禁用 CHG 时 DDSG 为低电平)

opt[2]= 1时、弱上拉至 REG1被启用

PIN_FXN1–PIN_FXN0[0~1]= 2、DDSG

这就是我们在 DCHG 引脚和 DDSG 引脚之间切换的方式。 例如、如果 DCHG 引脚和 DDSG 引脚都输出高电平、请将 CHG_OFF[bit2]= 1写入12.5.6 FET 控制寄存器(0x0097)。 DSG_OFF[bit0]= 0、因此 DCHG 引脚输出为低电平并且 DDSG 引脚输出保持为高电平。 在该操作之后、如果未读取第12.220节:FET 状态寄存器(0x7F)寄存器、DCHG 引脚将输出低电平、DDSG 引脚仍将输出高电平。 但在立即读取第12.2.2节:FET 状态寄存器(0x7F)寄存器后、DCHG 引脚和 DDSG 引脚都输出低电平。

因此、我们不能在写入12.5.6 FET 控制寄存器(0x0097)寄存器后读取第12.2.2节:FET 状态寄存器(0x7F)寄存器。 但是、一般的操作逻辑是在切换 MOS 输出状态后、将立即读取 MOS 输出状态以确认 MOS 状态输出受控。

您好、Max:

感谢您的答复。

很抱歉、我没有提供可让我们在同一页面上讨论问题的幻灯片。

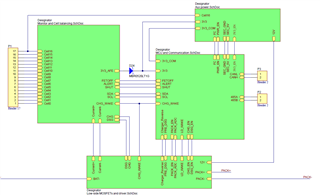

我们使用的是 低侧 MOSFET BQ76952原理图。 该参考设计由 TI 正式绘制。 请参阅下面的方框图。

DFETOFF 用作 AFE 的输入。 UC 将能够控制 DFETOFF 以打开/关闭 DFET MOS。

DDSG 和 DCHG 引脚用作 DFET /CFET MOS 的控制驱动器。

DSG 和 CHG 是悬空引脚。 (引脚43、引脚45悬空) nC。

我想随附详细的原理图供您参考。 您可以帮助找到我的附件低侧 MOS 吗?

TI 是否能够通过检查提供一种稳定的 FET 控制方式?非常感谢。

我想前面的讨论是在高侧 MOS 控制下。

e2e.ti.com/.../5807.Schematic.PDF

e2e.ti.com/.../5807.Schematic.PDF

此致、

戴夫