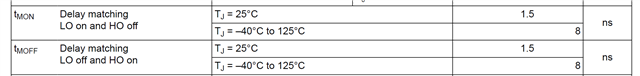

你好。 我有一个有关 LMG1205传播延迟匹配的一般问题。 数据表中指定了典型值和最大值、但没有指定最小值。

换句话说、如果我们的输入信号具有3ns 的死区时间、此死区时间是否会被栅极驱动占用并导致系统击穿? 栅极驱动器是否仅保证延迟匹配为正数、这意味着上升沿始终具有比下降沿更长的延迟?

谢谢。

开宇市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嘿 Kaiyu、

感谢您的提问。

为了实现延迟匹配、栅极驱动器不会占用3ns 死区时间。 如果同时在两个通道的输入端施加信号、则输出端的延时差为延迟匹配规格。 延迟匹配规格越低、击穿风险越低。 延迟匹配可说明通道之间的内部传播延迟的匹配程度。

但是、输入端的3ns 死区时间非常具有挑战性、您可能会看到由于栅极电阻器和 FET 等其他组件的寄生效应和参数导致的问题。

如果您有任何进一步的问题、请告诉我。

谢谢!

威廉·摩尔