请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC21750 您好!

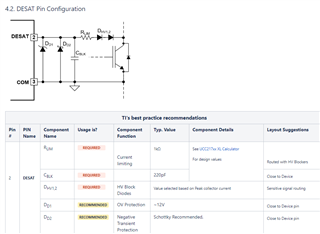

在测试 DESAT 保护机制时、我们发现放置在 OC 引脚上的齐纳二极管和散热二极管可能会稍微延长消隐时间。 当我们去除并测试时、我们发现了时间上的改进。 结果。 对于35A SiC MOSFET、SOA 受到限制、甚至可以节省50至数百纳秒的时间、这对我们非常重要。 因此、设计一个用于低额定电流 MOSFET 的去饱和电路是一项具有挑战性的工作吗? 由于上升电流的速率由电路板寄生电感决定、我们需要调整 DESAT、使其 SOA 对于给定电路板寄生的 di/dt 不应违反。 什么?

所以齐纳二极管和肖特基二极管是强制性的?

谢谢。此

致、 阿诺普