主题中讨论的其他器件:TPS3823、 TPS3828、、 TPS3824

大家好、

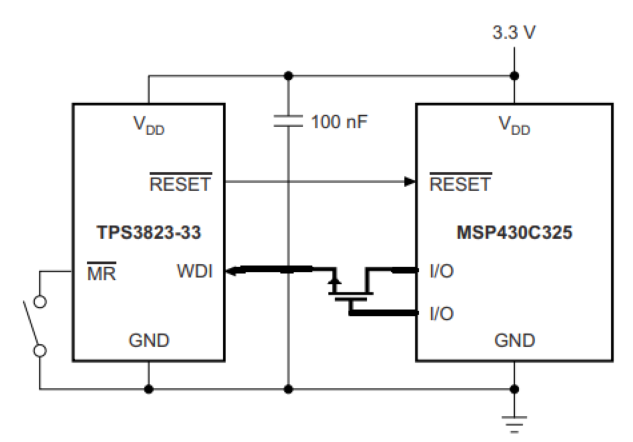

我的客户希望禁用 WDT、并在 MCU 发生读取/写入事件时将/RESET 设置为高电平。

在数据表中、显示当 TTOUT 的 WDI 中没有输入时、td 的/RESET 将为低电平。 但我的客户希望仅在特定情况下禁用此功能。

我想这可以通过以下特性来实现:

"可通过断开 WDI 引脚与系统的连接来禁用看门狗计时器。 如果 WDI 引脚检测到其处于高阻抗状态、TPS3820、TPS3823、TPS3824或 TPS3828将产生自己的 WDI 脉冲、以确保 RESET 不会置位。

您能否向我们展示禁用 WDT 的建议原理图/配置。 客户在 WDI 处使用 FET 并由 MCU 的 GPIO 控制它?

此致、

大桥