主题中讨论的其他器件:TPS65219

您好

我们在设计中使用 PMIC TPS6521908。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

我们在设计中使用 PMIC TPS6521908。

您好!

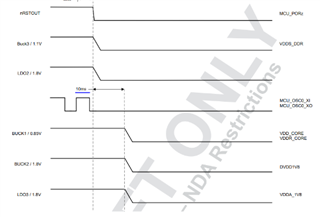

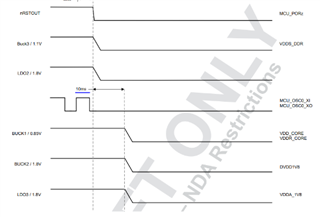

感谢您使用 E2E! 根据上述消息中提供的信息、电路板1执行 与 TPS65219匹配的有序断电序列 08 TRM 和板2在所有电源轨同时关闭的情况下立即执行断电。 影响下电序列的关键因素有四个:为 VSYS 供电的前置稳压器上的电压电平、外部电容/负载、 BYPASS_RAILS_DISCHARGED_CHECK 寄存器设置和任何故障。 由于您的设计中的问题似乎与定序顺序更多相关、因此我们可能会怀疑在 PMIC 完成断电序列或 PMIC 在断电 期间检测到故障之前 VSYS 上的电压会降至 UVLO 阈值以下。

您能否将 VSYS 电压添加到上一条消息中的示波器捕获中? 您在中断源寄存器(INT_SOURCE、地址0x2B)中看到任何中断吗?

要读取中断寄存器、您必须将使能引脚拉回高电平、以便 PMIC 可以转换为运行状态。

谢谢。

布伦达

您好!

感谢您的耐心! 立即或有序的断电并不影响 PMIC、但可能会对处理器的可靠性产生影响。 只要 VSYS 上的电压存在、PMIC 就会执行顺序断电、直到断电序列完成。 我建议与处理器团队核实不遵循 AM62的预期断电序列的后果(如果有)。 以下是处理器论坛的链接:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum

谢谢。

布伦达