您好!

我 正在查看数据表中提供的时序图、

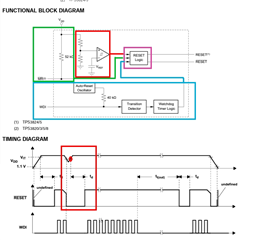

我注意到、它仅包括上电触发的复位和 WDI 触发的复位的时序信息。 没有关于 MR (主复位)方面的信息。

但是、在检查方框图时、我注意到此复位 IC 具有这三种触发机制、所有这三种机制都向复位逻辑块发送信号。

当查看由电压变化触发并导致复位的电路时、它看起来是一个比较器电路。 根据时序、当电压下降(导致运算放大器 OP 的输出为低电平)时、它会触发复位逻辑内的复位电路、从而产生复位输出。

不过、如时序图中的红圈所示、电压会迅速回升至正常电平、导致 OP 输出再次变为高电平。

从低电平转换为高电平时、复位逻辑的信号输入实际上非常短暂。

但是、RESET 输出在(T? + TD)时间。

这是否意味着当复位逻辑电路触发 RESET 输出操作时、复位逻辑块的运行不会受到外部 MR 信号变化的影响? 无论 MR 引脚的输入如何变化、它始终会完成固定复位时序。

从当前对电压变化引起的复位时序的理解来看、它似乎是这样工作的。

或者、激活复位功能后、MR 引脚的状态是否仍会影响复位输出? 例如、如果 MR 信号在复位信号完成 TD 时间之前被拉高、这是否会影响复位过程?