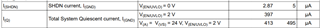

以下两种情况下的典型和最大静态电流是多少:

VBATT = 12V、VA = 0V、VOUT = 0V、EN/UVLO = 0V、VC = 0V、 VS= VSNS=VSW -由 VBATT Via10k 供电

VBATT = 24V、VA = 0V、VOUT = 0V、EN/UVLO = 0V、VC = 0V、 VS= VSNS=VSW -由 VBATT Via10k 供电

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

以下两种情况下的典型和最大静态电流是多少:

VBATT = 12V、VA = 0V、VOUT = 0V、EN/UVLO = 0V、VC = 0V、 VS= VSNS=VSW -由 VBATT Via10k 供电

VBATT = 24V、VA = 0V、VOUT = 0V、EN/UVLO = 0V、VC = 0V、 VS= VSNS=VSW -由 VBATT Via10k 供电

您好 Praveen:

我不明白这怎么可能、因为在共漏极拓扑中:

无论 EN/UVLO 状态如何、A、VS、VSNS 和 C 都直接有效地连接到 VBATT

然而、在共源极拓扑中:

只有 VS 和 VSNS 连接到 VBATT 通过10k 电阻器 A 和 C 是 开路

在我看来、这似乎是一个显著的差异、当它可用时、应该会导致低得多的静态电流、 未启用-即 EN/UVLO=0

您好、William、

根据定义、 器件的静态电流是启用器件时流出器件 GND 的电流。

禁用器件时测量的 GND 电流称为关断电流。

当 ENABLE 被拉至低电平时、没有电流流入 IC 的 A 或 C 引脚。 因此、CD 和 CS 配置的关断电流也将保持不变。

无论 CS 还是 CD 配置如何、VS 引脚上的电压都是相同的。 为 10k 电阻

器 可能会限制峰值静态电流(当 EN =高电平时)、但平均静态电流在有或没有 10k 电阻器。