主题中讨论的其他器件: TPS2663、 CSD19502Q5B、 TPS2490

你好。

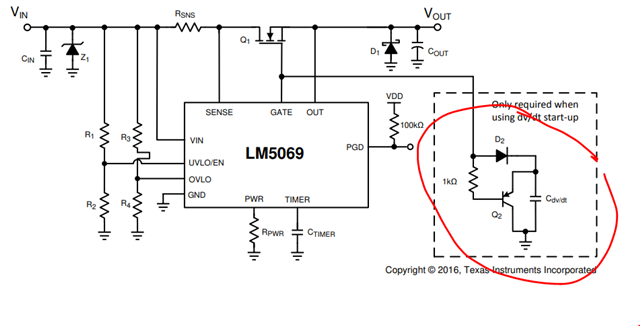

我们计划在如下配置中使用 LM5069:

-额定输入电压= 50V

-最大负载电流(脉冲电流、1ms 脉宽、20%占空比)= 12A

-输出电容= 1000uF

-最高环境工作温度= 75°C

-需要反极性(不是通过肖特基二极管,而是通过 MOSFET 本身,以最大限度地减少 IR 压降)

- UV / OV 保护为48V/52V

需要 dv/dt 启动来管理启动时的功率限制

器件输入端的 TVS 保护。

我们已查看 LM5069设计计算器。 但我们无法通过该脉冲电流确定正确的 MOSFET 选择来满足结温和 SOA 要求。 一旦 MOSFET 完全导通、应施加如上所述的脉冲负载电流。

您能对此提供帮助吗?