您好!

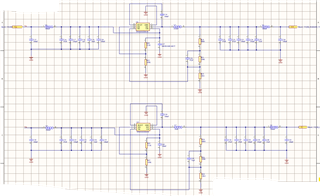

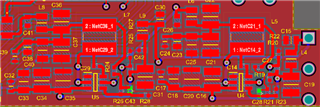

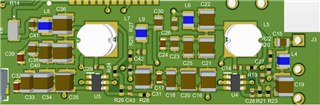

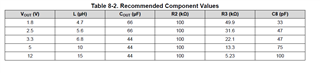

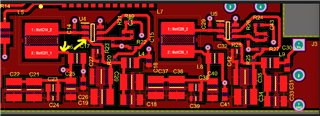

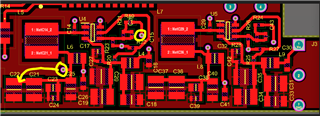

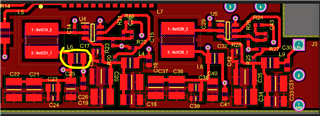

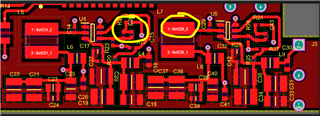

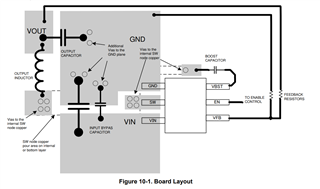

我在设计中使用了两个 TPS54302芯片、以便从共源 Vin (范围为7V DC 到24V DC、3A)生成两个电压源5V DC 和3V3 DC。

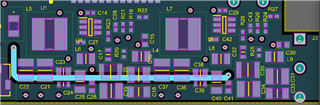

我完成了几项测试、发现可获得具有一些纹波的5V 直流和3V3直流(3V3大约40mV、5V 大约120mV)。

我注意到的问题有:

从这些电压源中汲取的电流不能超过200mA。

2-单独或同时从每个电源(5V 或3V3)汲取电流 会影响输出电平。 5V 更改为4.5V、3V3更改为3V。

我想问,这些问题有否解释,以及我如何解决。

谢谢。此致、

哈米德