请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS25940-Q1 主题中讨论的其他器件:TPS25940

您好、TI 团队。

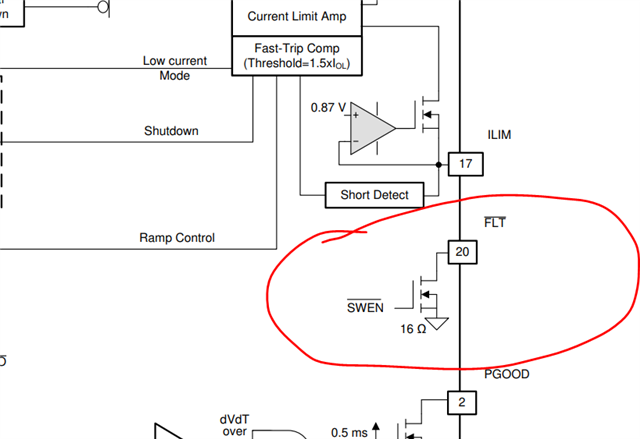

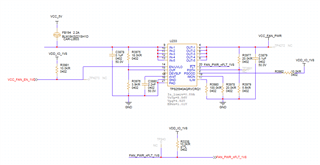

在平流过程中、我们观察到 Falut 引脚先后被拉低和拉高。 请在下方查找 TPS25940的原理图以供参考:

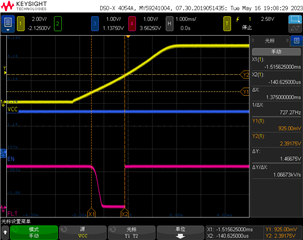

VCC (IN)、EN、FLT 的启动波形如下所示:

有关此压降的详细信息 如下所示:

您能否查看此行为、并确认它是否与数据表中提到的预期规范一致?

感谢您关注此事。