主题中讨论的其他器件:UCD90160

大家好、

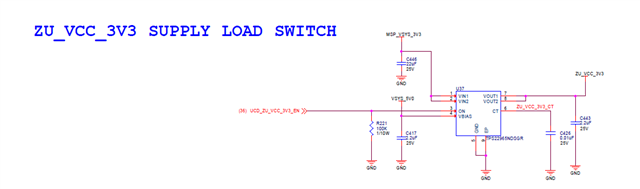

我们的定制电路板中有一个 TPS22965NDSGR 负载开关、并为其中一个 FPGA 电源轨供电。 负载开关的原理图如下所示。

在电路板上有一个 UCD90160电源序列发生器、可启用负载开关并监控输出电压(ZU_VCC_3V3)

配置 FPGA 后、电压会降至3V 以下。 因此、UCD 会检测 ZU_VCC_3V3的欠压、并根据故障响应关闭所有电源轨。

有时、当配置了 FPGA 时、UCD 会进入下电上电状态、因为 UCD 由同一 MSP_VSYS_3V3电源供电、并重新均衡 FPGA 电源轨、从而导致 FPGA 进入下电上电。

为了进行调试、我们使用外部工作台电源为 MSP_VSYS_3V3供电、并且我们观察到电压仍然降低到3V (即使由于 ZU_VCC_3V3电源轨欠压而没有关断、但 DIP 仍然存在)。

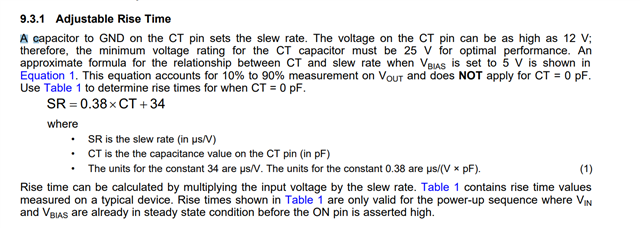

我们 使用了最大 CT 电容器 10000pF (0.01uF)来增加 Vout 上升时间、以避免浪涌电流、还遵循10比1的 Cin 与 Cout 比、以避免由于浪涌电流导致电压下降、如数据表中建议的。

这种浸液的可能性是什么? 此外、根据观察、这种骤降不是短期的、在整个时间内出现、即使在 FPGA 已配置并运行后也是如此。 配置 FPGA 时、在外部工作台电源上观察到的3.3V 电压轨电流消耗约为1.8A。

--

提前感谢

Kiran