Other Parts Discussed in Thread: TPS7A53

您好!

在我们的设计中、我想使用 TPS7A53作为低噪声参考电源、同时为 ADC、HF 模块和 MCU 等模拟器件供电。

系统架构:

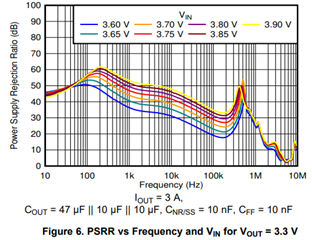

- TPS7A53前面的5.0V 隔离式降压转换器(最大组合纹波和噪声75mV 峰峰值)

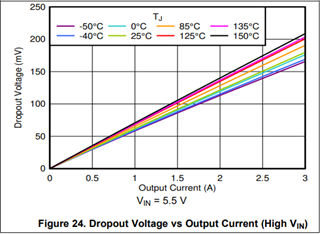

- 输出电压将设置为3.3V、因此压差为1.7V。

通读数据表时、这些器件似乎非常适合应用。

不过、我不确定这些器件是否能够在所有条件下正常工作、

- 大约2.1A 的最大峰值功率组合

- aroun 10uA 的最小功率。

关于这些要求、我有以下问题:

- TPS7A53能否在此类低功耗输出(10uA)下仍能正常工作?

- 有人能指出我的"丢失"电流@10uA 吗?

第二期:

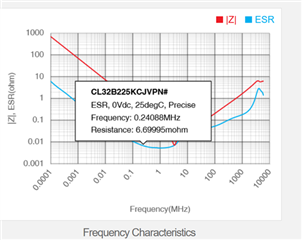

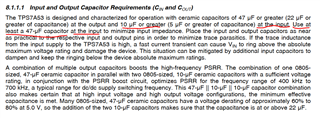

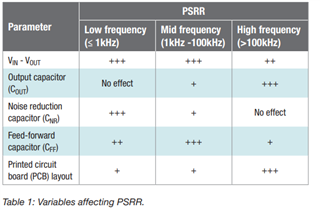

该降压转换器具有240-320kHz 的开关频率。 为了过滤这些高频纹波、输出端的最佳电容器选择是什么?

提前感谢您!

此致!

安迪