请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM61460 主题中讨论的其他器件: LMR33630、

您好!

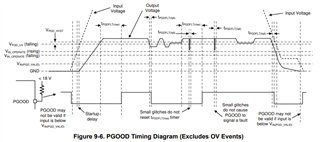

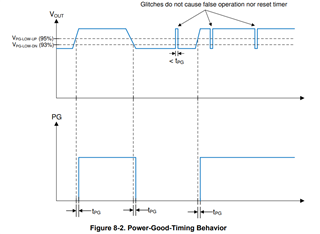

我感到困惑为什么6A LM61460 PG 抗尖峰脉冲时间远低于 LMR3352的 PG 抗尖峰脉冲时间? 为什么 LM61460的上升抗尖峰脉冲时间远高于 LMR33630? 有什么注意事项吗? 我认为它对实际上电或复位没有影响。 谢谢!

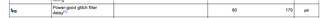

LMR33630 60-170us 的 PG 上升和下降时间

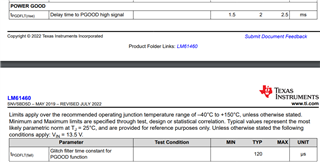

LM61460上升2ms、下降120us

-A