主题中讨论的其他器件: CSD17313Q2

您好!

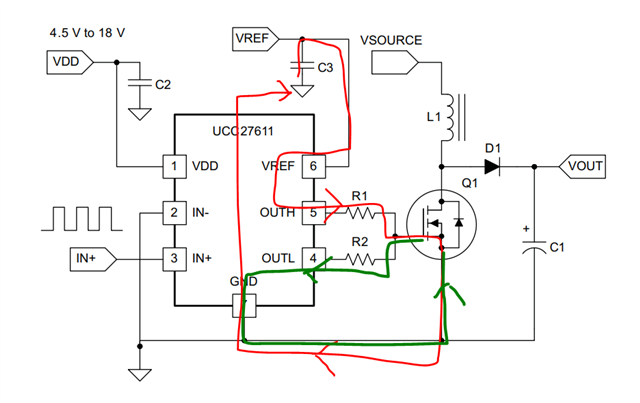

我正在使用 UCC27611驱动 GaN FET (EPC2204)。 我的电流设计中的上升和下降时间与数据表中的时间不匹配。

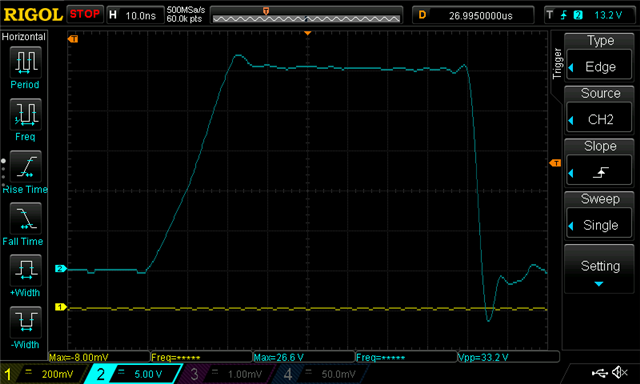

我确实得到了5ns 的下降时间、但是上升时间 大约为20ns。 我需要<10ns 的上升时间才能使我的应用正常工作。 我已经尝试将栅极电阻器降低至0欧姆、但遗憾的是、20ns 上升时间仍然是我看到的最佳选择。

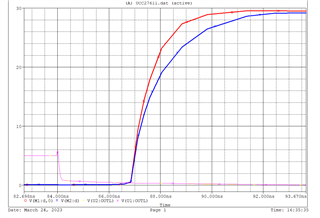

我使用5V 的 VDD 为 UCC27611供电。 我怀疑这可能是导致上升时间缓慢的问题。 对于列出的大多数规格、数据表似乎使用了 VDD 12V。 VDD 是否对上升和下降时间有影响? UCC27611是否有详细说明 VDD 与上升/下降时间的图或任何额外数据?

在 我重新设计电路之前、我想确认将 VDD 升高到12V 或更高会将上升时间缩短到<10ns。

谢谢!