请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:BQ21062 您好!

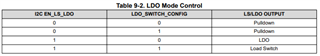

我们的设计中使用的是 BQ21062。 我们将 VINLS 连接到 PMID、将 LS/LDO 连接到 VINLS、因为我们没有使用 LDO 功能。 遗憾的是、在这种配置中、有高电流流经、电池消耗、因为我们不知何故错过了表9.2。 如果 LDO 未被使用、似乎有一个内部下拉。 到目前为止、作为权变措施、我们使系统进入负载开关配置、并接受由于启用 FET 而可能产生的额外电流消耗。 对于下一个硬件布局、我们考虑 将 VINLS 和 LS/LDO 分流、但不要将它们连接到 PMID (必要时、我们可以 在 VINLS 和 GND 之间放置一个1 µF 电容器)。 这是否正常工作或者 VINLS 是否始终必须连接到 PMID?

非常感谢您提供任何帮助、

马克