您好!

该线程得到了解决、但正确的答案是、必须增大 MOSFET 的电网电阻以避免出现问题。

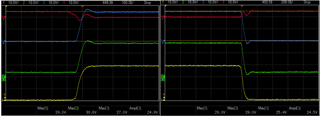

我添加了12欧姆的电网电阻器、并且得到该结果

顶部 MOSFET/Ch2 BOOT 引脚/Ch3相引脚/Ch4底部电网 MOSFET 的 CH1电网

顶部 MOSFET/Ch2 BOOT 引脚/Ch3相引脚/Ch4底部电网 MOSFET 的 CH1电网

所以相电压过高、

我将电网电阻增加到120欧姆、

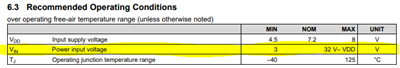

不再有过冲、但相电压始终为高电平。 有关 TPS28225的 VDD = 5V 和顶部 MOSFET 的漏极= 24V 的信息、请参见

最大相位引脚应该为27.9V - 5V + 0.3V = 23.2V。 相位引脚上的最大电压测量值为23.7V

我的相电压是否对 MOSFET 驱动器至关重要? 如果是这样,我怎么可以编辑它?

感谢您的帮助