我公司用1片 TPS53353同时为两片 XC7K325T-2FFG900核电压 VCCINT1V0供电(精度±3%),总电流需求预计约为15A,工作过程中出现巨大电压波动(max:2.4V),发生几分钟左右, 没有找到具体的法律,原因是什么,还是造成这种波动的原因,如何解决?

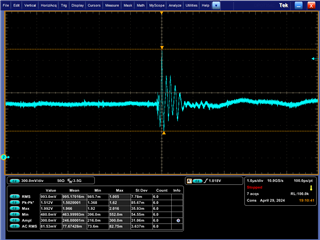

测试波形如下:

原理图如下:

祝你一切顺利!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

观察您共享的波形、我们可以看到6.67MHz (3个子分部中的4个周期@ 1μs /分部=每周期150ns)处出现谐振。 由于 TPS53353的开关频率为500kHz、因此这不太可能来自 TPS53353。 如果这每几分钟发生一次、初始脉冲下降、则可能会突然出现负载脉冲、从输出电容器中抽取能量、并激励布局电感和一些输出电容器之间的谐振。

470μF 聚合物电容器甚至47μF 陶瓷电容器在6.67MHz 处不太可能仍然是电容、因此 XC7K325T-2FFG900上的0.1μF 电容器或某些输入旁路电容很可能会与布局电感发生反应。

1) 1)检查0.1μF 电容器的自谐振频率、如果它们的自谐振频率为6.67MHz、或者非常接近、它们可以是自谐振频率。 而不是使用3个相同的电容器、将一个从0.1μF 更改为0.33μF、将另一个更改为33nF。 这将传播其自谐振频率而不进行扩展、因此会引入电容间谐振频率、这可能有助于减少此频率。

2) 2)如果在6.67MHz 中找不到您当前正在使用的具有自谐振频率的电容器、您还可以查找小型封装(0201或0402) 电 mΩ、其自谐振频率非常接近6.67MHz 并具有几百或更高的 ESR、可在 XC7K325T-2FFG900的输入端充当谐振旁路。 ESR 的200 + mΩ 可用于自抑制谐振、同时匹配电容器的自谐振频率、这有助于在影响 XC7K325T-2FFG900之前将振铃能量分流到地。

您好、非常感谢您的反馈、接下来我们将根据您的意见进行实验、对于我们的 TPS53353原理图设计、我发现了一些问题、我不知道是否需要修改?

Shuda、您好!

VDD 引脚没有单独的4.7uf 电容接地,但与 LL 引脚共享去耦电容,是否需要单独添加4.7uf 电容?

是的、VDD 引脚应具有专用的4.7uF 电容、并且在布局过程中应靠近 VDD 引脚放置。

LL 电感值为1uH、实际 Webench 建议的电感值约为0.44uH、电感值是否需要使用0.44uH?如果使用1uH 有什么影响?

是数据表建议使用1uH、因此请继续使用1uH。 需要查看 WEBENCH、了解为何建议使用0.44uH。

去耦电容器使用4个47uf 和3个0.1uf 陶瓷电容器,这些电容器放置在靠近 LL 引脚的位置。 是否应全部移除47uf 和0.1uf 电容?

这些电容是否靠近布局中的 LL 或开关引脚? 这就是您的意思吗? 如果是、SW 噪声会耦合到输出中。 请遵循数据表布局指南、检查是否放置良好。

根据数据表、输出电容实际上过大。 它需要限制在220uF 或更低、并且典型值为3x22uF。 因此、需要移除 E12和 E13 470uF 电容器。 这可能会降低 ESR、因为47uF 电容器看起来是陶瓷电容器。 不过、您可以添加纹波注入 RCC 网络、其值可以使用设计计算器工具进行设计。

您公司的设计计算 Excel 有两个红色警报(ESR_MIN_STANCE 和 Vo_undershoot),我不知道如何将其设计为一个[/报价]看起来红色单元格表示未满足最小 ESR 要求。 您需要使用设计计算器设计电感器到 FB 的 RCC 注入网络。

谢谢。

阿莫德