工具与软件:

您好!

我们具有采用 LM5122的升压器设计、并且在 ATP 后我们会收到一些损坏的器件。 ATP 期间的馈电电源提供20V 电压、电流限制设置点为3A。 上电后立即发生故障。 PSU 的设计数据如下:

- Vout = 66V(最大值) 0.8A (大约50W 输出功率)

-输入电压= 18-33V (典型值28V)

-开关频率约为210kHz.

-通过感应电阻器的初级电流限制设定点大约5A (0R015 )。

设计工作原理正常。 但是、当为实验室电源提供电流限制设置点为3A 且远低于 DUT (5A)的电流限制时、我们面临 PSU 无法正常启动的问题、因为输入电压下降。 这种行为是可以的。 问题是对于某些单元、功率元件发生故障(低侧开关 MOSFET)和 PWM 控制器(LM5122)。PWM 控制器故障模式和影响似乎不同。 有时 SW 节点与 AGND 之间存在短路。 另一个影响是 VCC 引脚对地短路。

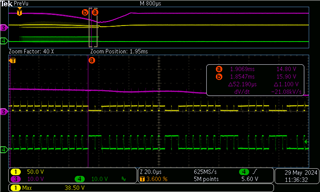

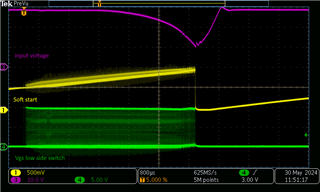

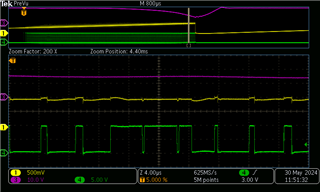

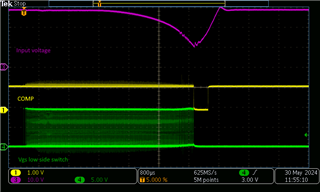

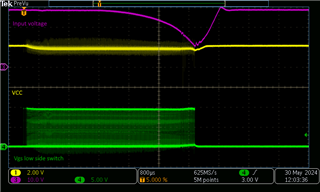

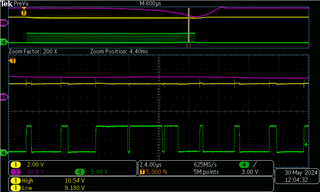

我测量了这种情况下的启动情况(Vin=20V、3A 电流限制设定点)、并发现有时低侧导通时间相当长、这是我不明白的(请参阅下面的屏幕截图)

如果由于馈送电源的电流限制设置点过低而达到 UVLO 阈值、则首先完成从上电到第一个开关的序列。

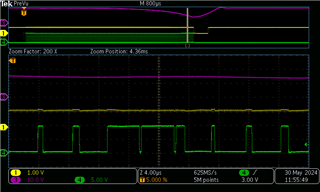

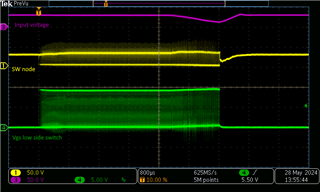

下图是正常切换的细节。 需要注意的是、脉冲宽度随时间的增加而增加、

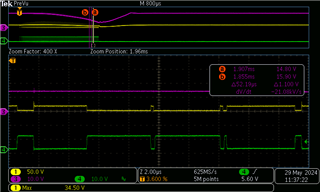

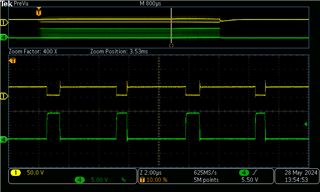

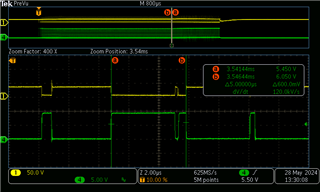

下一个图:细长脉冲宽度不可避免:

请注意、对于详细的屏幕截图(2-3)、我已关闭通道3、以重点关注最重要的信号。

首先、周期时间要比正常情况下长、其次是短关断脉冲。 该缩放区域的输入电压没有下降。 实际上、在这种情况下、我无法看到损坏案例。 不过,我有以下问题:

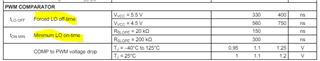

Q1:LM5122在启动(电压斜升阶段)期间生成的最小和最大脉冲宽度是多少?

问题2:什么原因可能导致上一屏幕截图中显示的异常长导通脉冲?

Q3:LM5122内部逻辑/状态机是否有可能被切断并永久地控制低侧 MOSFET?

当然,启动应在给水供应的适当电流限制下进行。 但是、我绝不会期望器件发生故障(PWM 控制器本身或开关 MOSFET 之一)。

提前感谢!

安德烈亚斯