你(们)好

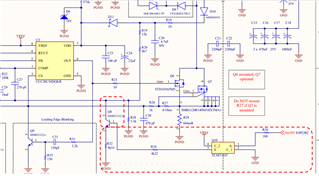

我已按照下面数据表第26页中的典型应用示例和设计指南行、使用 UCC28C54进行设计。 请参阅随附的原理图。

除了输出电压大幅下降且在输出范围内始终保持稳定之外、它似乎能够按预期工作。 请参阅随附的输出电压图。

为什么电压下降这么大、对此有何解决方法?

T1为1.55mH、NPS = 9.67、NPA = 7.73

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我已按照下面数据表第26页中的典型应用示例和设计指南行、使用 UCC28C54进行设计。 请参阅随附的原理图。

除了输出电压大幅下降且在输出范围内始终保持稳定之外、它似乎能够按预期工作。 请参阅随附的输出电压图。

为什么电压下降这么大、对此有何解决方法?

T1为1.55mH、NPS = 9.67、NPA = 7.73

谢谢!

您好、Thomas:

-为什么要在隔离栅上使用光耦合器? 根据原理图、您将使用 PSR (初级侧调节)、通过分压电阻(R19、R20和 R28)通过辅助绕组到达 FB 引脚。 因此、不需要 SSR (次级侧调节)。 请从 FB 引脚断开 Q8、或从转换器上移除光耦合器并检查问题是否得到解决。

Q7在 Q6的漏极和源极之间连接的原因是什么?

-D8齐纳二极管已连接以进行保护? 这没什么问题、请记住、它会耗散一些功率。

谢谢你

曼努埃尔您好

感谢您的答复!

Q10、Q8和相关电阻器未安装。 抱歉、该数据不应出现在原理图中。

正常工作期间 VDD 为15伏、因此 D8不应耗散任何功率。

Q7对于 Q6是可选的。 在本例中、按照原理图中所示安装 Q6。

Q7用于将来/实验与更高电压 TVS 缓冲电路配合使用、以提高较低/中等负载下的效率。 但首先、具有 RCD 缓冲器的一般设计需要正常工作。

Brgds、Thomas

您好、Thomas:

-您的转换器设计的最大负载是多少? 您的主电感器是否设计为该功率级别? 通过收集的数据、我看到您进行了测试 Iload=9A (Pout=108W)。 如果转换器过载、控制器可以进入电流模式、然后输出电压将超出稳压范围。 请根据以下公式验证您的电感值。

在针对满负载时的功率级别验证电感值后、请在满负载时获取(VDD - PGND )、(CS- PGND )、(DRV- PGND )和(VOUT - GND )。 将触发器置于 VDD 通道 Rising、THRESHOLD UVLO (14.5V)上、并使用1/FSW 的时间标度、其中 FSW 是开关频率(80KHz、根据您的 RT/CT 值)。 满载时的这些波形将告诉我们控制器是否存在任何故障。 但首先验证电感器值。

谢谢你

你好、Manuel

很抱歉耽误你的时间很长。 我们设计了新的 PCB 布局和新的定制变压器、以改善漏电感。

但是、我们的问题仍然存在、我倾向于某种干扰、而不是原理图设计问题。 不过、我已尝试遵循数据表中的所有 PCB 布局设计规则和建议。 我 下面查看 Q 版的数据表、因为应用设计与我们的非常相似、我发现数据表更全面、更详细。

请根据需要找到随附的波形、以及一些我认为可能有用的额外波形。

另请注意、波形是在5A 负载而不是7A 时记录的、原因是我们在5A 时具有最高功率。

我想可能是 Comp 上的干扰导致了这些问题。 我尝试了几个不同的事情,试图抑制这些,但没有成功。

我还进行了负载阶跃变化测试、类似于数据表中的250mA -> 2、7A 阶跃负载变化、并观察了 Comp 波形、在我们的情况和数据表中看起来非常相似、与数据表相比、我们的情况下信号上没有更多的不平衡。 但这可能没什么大不了的。 我将在另一篇文章中添加该波形、因为我刚刚意识到、但没有保存该波形。

我真的很感谢在这方面的帮助,因为我觉得我已经尝试了"一切"。

谢谢! Thomas

很棒、希望你有一个美好的周末!

同时又更新了一个。

我进行了一个"微小"的设计更改、将 PGND 和 GND 连接在一起、将 VAUX 从 FB 断开、而将 Vout 连接到 FB。 因此、我将设计从隔离式拓扑更改为非隔离式拓扑。

然后,它就像一个迷人的瞬间。 12.9V 的空载电压在满载7A 时降至仅12.5。 我的最大压降目标中。

因此、在我看来、问题在某种程度上与来自 VAUX 的反馈信号有关、我假设存在干扰。

问题是、我哪里出了问题、如何解决?

谢谢、Thomas