工具与软件:

大家好、我们将 LM74810MDRRR 用作热插拔/理想二极管控制器。 我们将遇到以下问题:

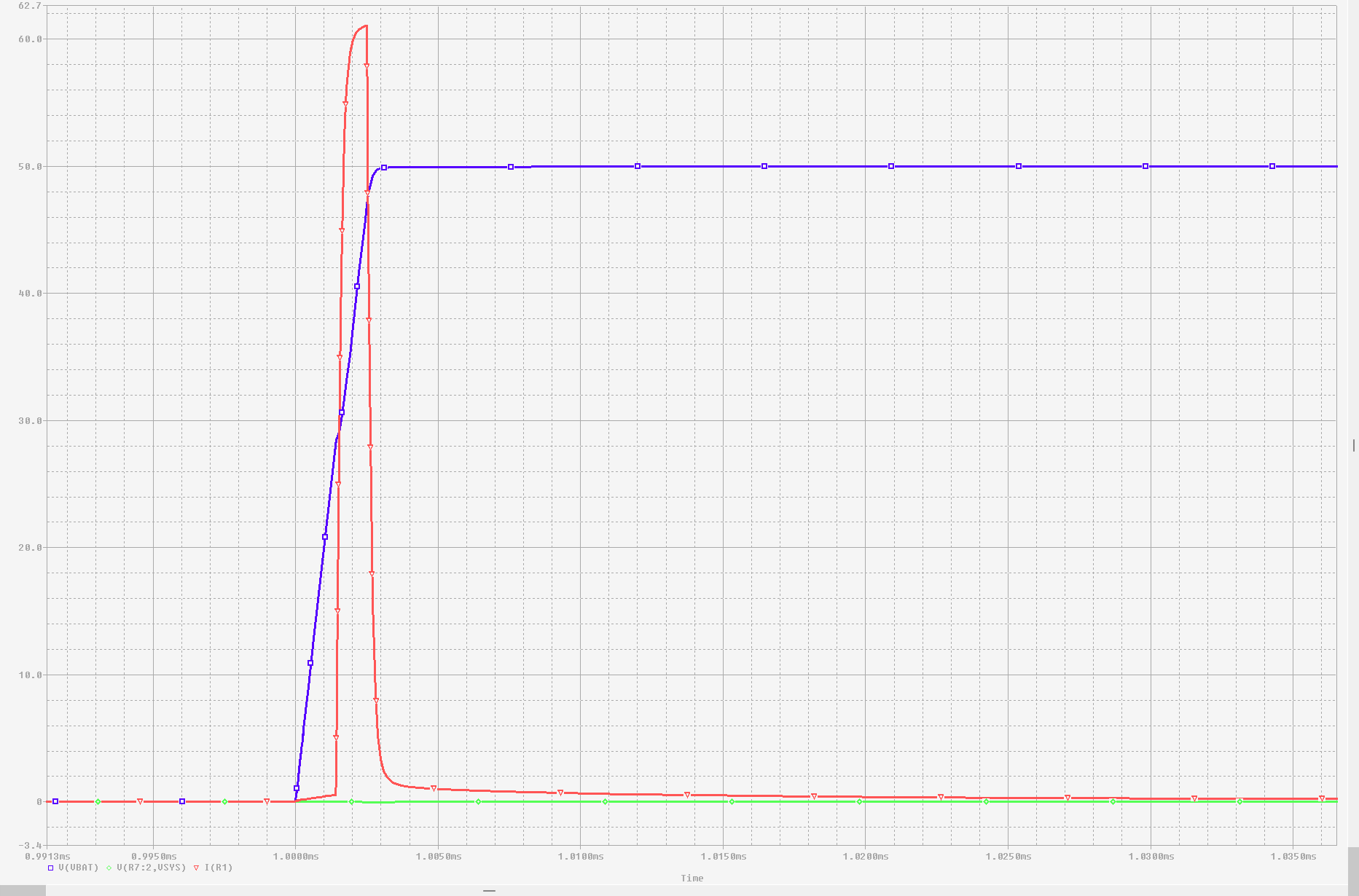

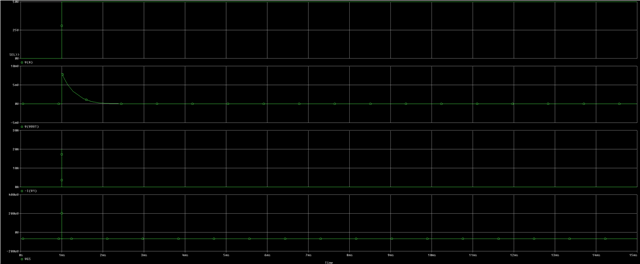

当 EN/UVLO 被拉至低电平(禁用)时、我们会在热插拔50V 电源时看到很大的电流。

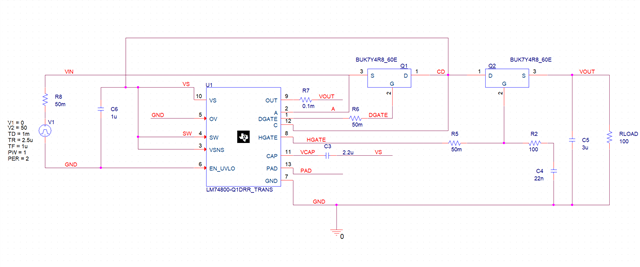

2.我们在所有接触输入轨的电容器上都有串联电阻、但我们看到 IC 在插入后会损坏。 似乎有一条通过 C/A 引脚连接到 C67的电荷泵电容器的电流路径。 请参阅随附的图像

当我们在评估板上看到这个时、我们也会看到热插拔器件时的电流高得多。 电流约为3-4A、将电容器的串联电阻更改为100 Ω。

我们需要考虑 IC 是否有内部电容?

是否有办法限制这种浪涌?

我们是否可以在不影响理想二极管运行的情况下向 A/C 迹线添加串联电阻器(例如添加100 Ω)?

谢谢!

Peter Davis