工具与软件:

尊敬的 TI 专家:

LM5146能否与 VG (th)低至最小1.1V、但可提供极好 Qoss 和 Qrr 的逻辑电平 MOSFET 配合使用? 例如 Infineon MOSFET BSC070N10LS5。 该 FET 与 LM5146在设计中有何注意事项?

在 LM5146快速入门工具中、为什么底部 FET Coss 和 Qoss 损耗计入顶部 FET?

谢谢

新生儿

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 TI 专家:

LM5146能否与 VG (th)低至最小1.1V、但可提供极好 Qoss 和 Qrr 的逻辑电平 MOSFET 配合使用? 例如 Infineon MOSFET BSC070N10LS5。 该 FET 与 LM5146在设计中有何注意事项?

在 LM5146快速入门工具中、为什么底部 FET Coss 和 Qoss 损耗计入顶部 FET?

谢谢

新生儿

你好、Neo

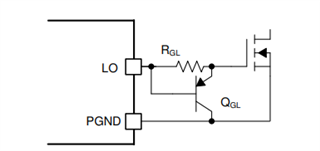

安装100kOhm 下拉栅极电阻器是一个好主意、这有助于 防止在器件未通电时意外导通。

当器件通电且稳压器正在开关时、如果 使用栅极电阻器、填充 PNP 晶体管有助于防止 SW 节点 dV/dT 意外导通。

如果 LO 布线直接连接到 MOSFET、则从 LO 到 MOSFET 的连接必须尽可能短、以减少串联寄生电感

我离开办公室后、我将无法再回复此 E2E 帖子。

如果您仍在尝试解决此问题、请勿回复此帖子、而是创建一个新帖子、以便快速从其他工程师处获得帮助。

- EL

- EL