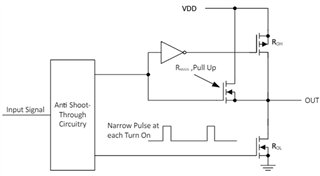

TI 的栅极驱动器采用上拉和下拉结构来驱动输出级。 上拉结构提供拉电流以开启功率器件、下拉结构提供灌电流以关闭功率器件。 图1 所示为栅极驱动器的典型输出级:

图1:具有混合上拉结构的栅极驱动器的输出级示例

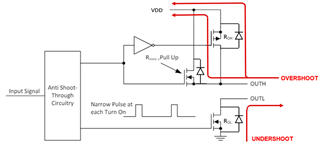

栅极驱动器要求输出电压处于安全水平之内、以防止损坏输出级。 通常、输出电压不应超过 VDD 或低于 GND (有关规格、请参阅栅极驱动器数据表的绝对最大额定值部分)。 如果输出经历过压、电流可以通过上拉结构的体二极管从输出引脚流向 VDD。 如果输出端发生欠压、电流可以通过下拉结构的体二极管从 GND 流向输出引脚。 流经这些路径的大电流可能会导致电气过载、并可能损坏驱动器。 图2 所示为在超出器件规格的输出过压或欠压期间的电流路径图;还包含 MOSFET 体二极管:

图2:输出过压或欠压事件期间的电流路径

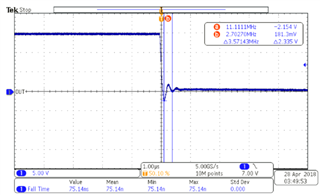

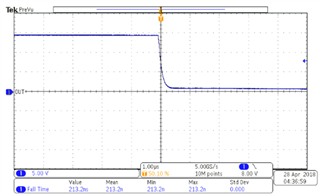

在许多情况下、输出过压或欠压是由于高 dV/dt 和 di/dt 引起的振铃引起的、高 dV/dt 和 di/dt 是由栅极驱动器的快速开关引起的寄生电感和电容引起的。 适当的 PCB 布局对于限制寄生效应非常重要(布局指南可在栅极驱动器的数据表中找到)。 除了布局之外、一个简单的解决方案是增加栅极电阻或将外部栅源电容器放置在靠近器件的位置。 这两种解决方案都可以通过减慢上升/下降时间来抑制振铃。 图3和4 分别显示了具有和不具有栅极电阻的栅极驱动器的输出信号:

图3:无栅极电阻的输出信号

图4:具有栅极电阻的输出信号

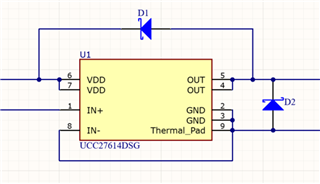

另一种解决方案是在输出引脚上添加二极管。 这些二极管用于钳制输出电压、防止超过二极管的正向电压、并为多余的电流通过提供除内部体二极管之外的路径。 通常使用肖特基二极管、因为它们具有大约0.3V 的极低正向电压。 快速正向恢复时间也是选择二极管时需要考虑的另一个规格。

图5 显示了二极管相对于栅极驱动器引脚的放置原理图。 假设两个二极管具有相同的正向电压(Vf)、如果输出电压超过 VDD + Vf、则 D1将导通、过量的电流会流入 VDD。 如果输出电压小于 GND–Vf、则 D2将导通、过大的电流通过 GND:

图5:输出钳位二极管

需要将输出电压限制在栅极驱动器的规格范围内、超过此规格可能会损坏器件。 适当的布局、栅极电阻、外部 CGS 和钳位二极管都有助于降低输出过压和欠压、并避免潜在的损害。