工具与软件:

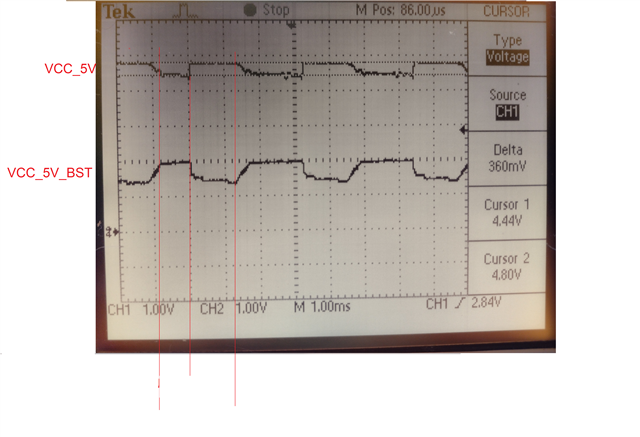

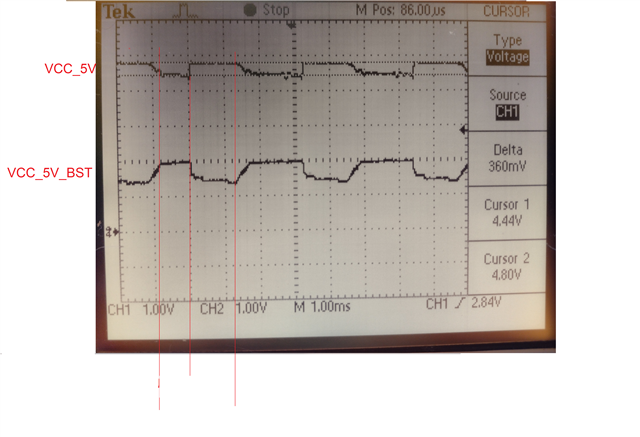

当达到欠压限值(本例中为4.4V)时、 TPS25944L 似乎会限制电流输出、但不会将 FLTn 置为有效或将输出锁存。 相反、输出(VCC_5V_BST)再次开始斜升、这会导致输入(VCC_5V)再次下降、从而导致另一个 UVLO 事件。 这就产生了一个恒定的循环、从不恢复或锁存至故障状态。 为什么故障状态不被锁存? 可以采取什么措施来强制这达到锁存条件? 下面是连接到其输出的电子保险丝和直流/直流的原理图。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

当达到欠压限值(本例中为4.4V)时、 TPS25944L 似乎会限制电流输出、但不会将 FLTn 置为有效或将输出锁存。 相反、输出(VCC_5V_BST)再次开始斜升、这会导致输入(VCC_5V)再次下降、从而导致另一个 UVLO 事件。 这就产生了一个恒定的循环、从不恢复或锁存至故障状态。 为什么故障状态不被锁存? 可以采取什么措施来强制这达到锁存条件? 下面是连接到其输出的电子保险丝和直流/直流的原理图。

尊敬的 Arush:

感谢您的答复。 我将 R19更改为180K、因此 UVLO 设置为4.4V。 我同意,这看起来不是正常的,但我一直无法确定根本原因,我希望你可以帮助我. 随附了更新后的原理图、其中显示了我所做的更改。 我还将包含3个新波形、说明 IMON 相对于 VCC_OUT (原理图中的 VCC_5V_BST)和 VCC_IN (原理图中的 VCC_5V)的变化。 ILIM 设置为1.7A、因此我认为这是欠压情况、而不是过流情况。 当我强制过流时、我看到正常的故障事件(VCC_5V_BOOST 变为低电平、FLT 变为低电平)。 但每个欠压条件都会始终进入此循环模式。 我曾尝试将 dVdt 更改为开路并更改为0.1uF。 它会改变波形、但在两种情况下都存在循环。

我还可以检查或测试循环以确定原因、而不是直接进入故障状态?

谢谢!

Rick