工具与软件:

您好!

我叫 Pritam、 Google 半导体团队的一名成员。

我将 TPS22997负载开关用于其中一种评估板设计、主要用于创建上电序列。

但我观察到、当负载开关偏置(提供了 VBIAS = 5V)且负载开关启用(ON 引脚为高电平)时、但当 VIN (输入)悬空时、输出端会出现泄漏。

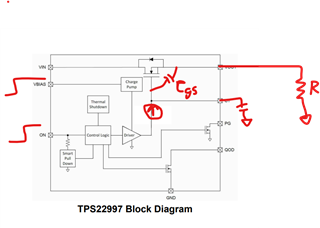

我向 BIAS 引脚提供5V VBIAS。 向负载开关提供 VBIAS 后、我将 ON 引脚置位(高电平)。 但是、输入引脚(VIN 引脚)悬空...因为在中、还没有向 VIN 引脚提供输入。

在该状态期间、我注意到输出引脚(VOUT)电平稳定增加、并不断增加、直到我提供 VIN (输入引脚不再悬空)或将 ON 引脚设置为低电平(或移除 VBIAS 5V)。

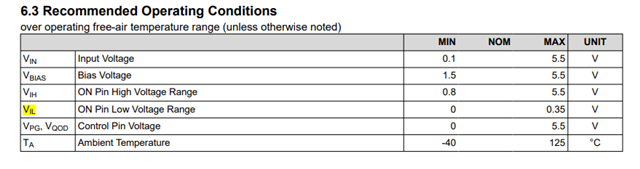

当 VIN 引脚悬空(VBIAS = 5V 且 ON 引脚为高电平)时、负载开关是否预期会出现此行为? 数据库不能真正指定这种特定情况下的行为。 我知道这可能不是 TPS22997的预期操作。 但是、我想了解是否会出现这种观察结果。

如果是、该泄漏来自哪里? 当 VIN 悬空(但 VBIAS = 5V 且 ON 引脚为高电平)时、该漏电流是否来自 VBIAS? 谢谢。

供参考:我已在负载开关上连接了一个小片段。