Other Parts Discussed in Thread: UCC27614

工具与软件:

尊敬的主员工:

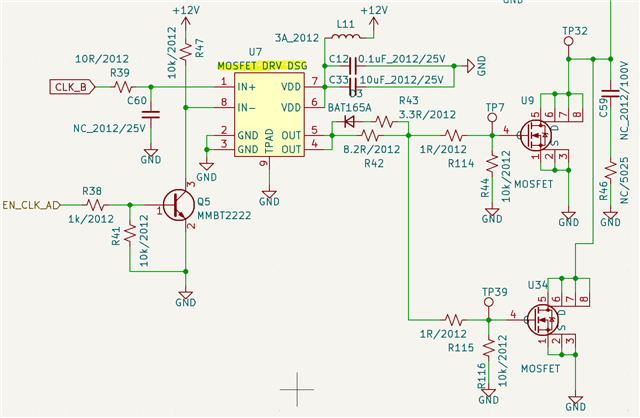

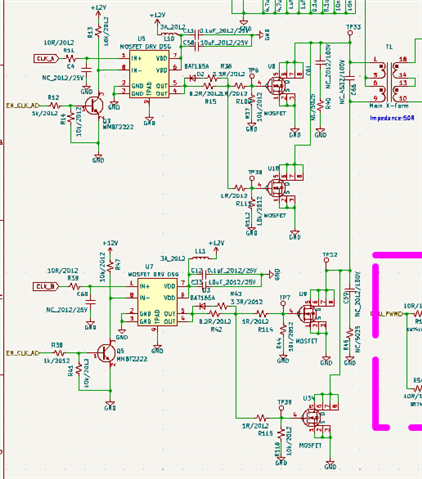

我使用的是 UCC27614 8引脚 SON DSG 封装。

■UCC27614工作条件。

-工作频率 :500kHz/300kHz.

- FET : BSC146N10LS5并联驱动。

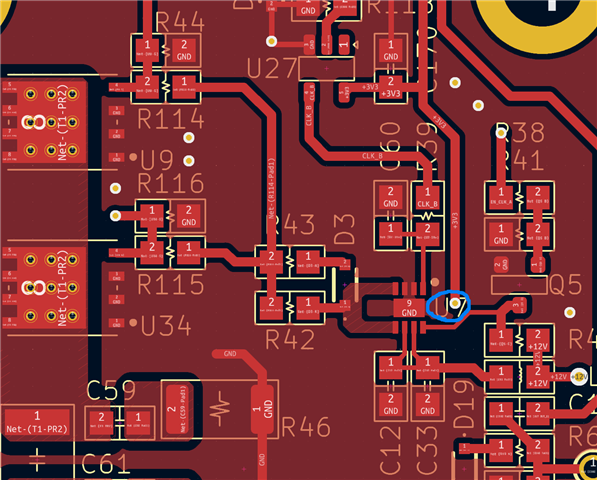

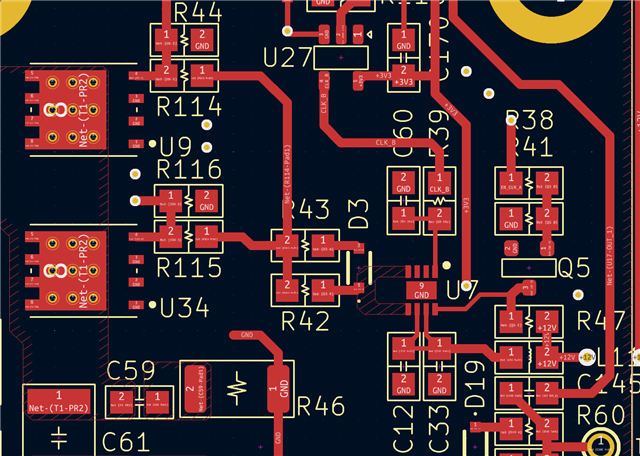

-示意图和图案:见下文。

- 1.6T 2层 PCB。

-故障: 1印刷电路板有 故障。

1 PCB 运行异常。

你能告诉我出什么问题吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

亲爱的耶米。

感谢您的快速响应。

1) L11: MH2029-800Y

www.mouser.kr/.../mh-777565.pdf

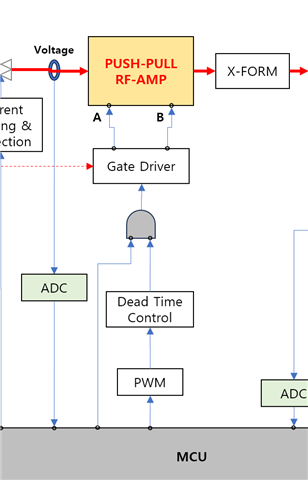

2) CLK_A、CLK_B 是推挽式 RF-AMP。

3) 3) CLK_A、CLK_B、EN_CLK_A 信号由 MCU 控制。

-第一。 系统开启时、VDD (+12V)始终开启。

-第二。 当用户启动时、CLK_B 打开。

-最后一个。 EN_CLK_B 为高电平。

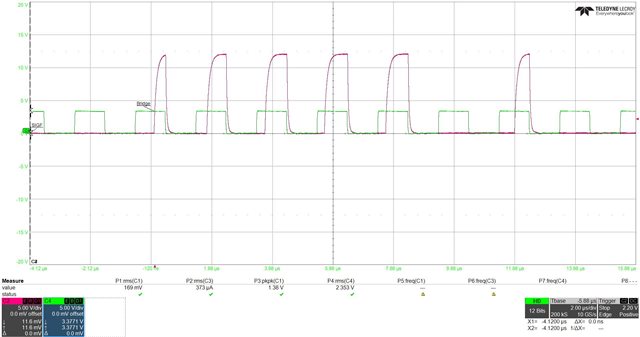

请参阅下面的波形。

※C2(品红色): clk

C4 (绿色):启用。

尊敬的 Sanghyun:

感谢您在周末的耐心等待。

我们来看一下、EN-CLK-A 变为低电平、输出关闭、可能会影响输出波形。 但是、我想进一步澄清一些问题(对于请求不够具体、我深表歉意!):

谢谢!

耶利米

感谢您的答复。

我同意 VDD 上存在很多噪声。

但 VDD 信号始终保持在11Vdc 以上。 我认为这种噪音不会影响错误操作。

我已经经历了两次失败与这个 IC。

第一次、 IC 没有任何 OUT 信号。 所以我更换了它。

第二个是 异常操作、如 上图所示。 (我保留了 这个错误的操作示例)。

此采样首次运行良好。 我不知道这种情况何时发生。

我有2个问题。

1)清除栅极驱动器输出信号与 GND 之间的信号。

- UCC27614 SON DSG 封装太小。

我担心 输出信号与接地之间的间隙。

2)内部逻辑。

- 是否有任何问题从他人的索赔这个 IC ?

是否存在 EN/IN-、IN/IN+引脚的序列?

如上图所示、 在应用 IN/IN+引脚信号(时钟)后、EN/IN-引脚被激活(低电平)(第八张图)。

或者您是否检查内部逻辑?

如果此问题的原因是间隙、我将更改 SOIC 封装。

如果没有、我不能肯定这种问题不会再发生。 (我还可以更改 IN-、IN+的顺序)

我需要您和贵公司专家组的帮助。

此致。

尊敬的 Sanghyun:

对于您刚才报告的第三个问题、您能否发送一个波形并告诉我们该波形是在启动时还是在启动后一段时间后我们看到断电?

至于其他问题、在正常工作条件下、DSG 的性能应与 D 封装相似、并具有良好的布局。

你在8月5日发送的照片2和3似乎没有任何异常有关他们。 您能否尝试一些降噪建议、看看有问题的行为是否仍然存在? 此外、您可以尝试切换到 D 封装、并查看该 SOIC 封装是否发生了相同的故障。

谢谢!

耶利米