工具与软件:

您好!

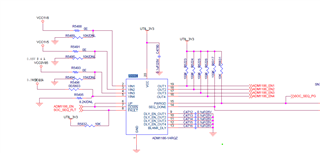

我们 在 eNodeB 设计(LTE- 4G)板中使用 TPS564242。

启用来自以下 IC

问题是、 即使在使能引脚为高电平之前、稳压器也会提供输出。

另一个问题是、即使断电、输出也不会变为0V。 在相当长的时间内、输出保持在1V。

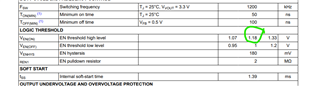

我们尝试了为 R6029放置50k 电阻(根据数据表、将 VEN1阈值保持在1.18V)、以便在使能端为高电平之前输出为0V。 但我们观察到输出为1.27V。

它不会达到1.8V。

移除了100uF 电容器、在输入和输出端仅放置了22uF 电容器两个 nO。

基本来说、要求输出在将使能施加为高电平之前应为0V、只要使能关闭(即电源关闭)、输出就必须变为0V。

电路板具有 FPGA、它由此稳压器供电。

我们可以观察到 FPGA DONE 引脚在配置后将为低电平。 实际上、DONE 引脚在配置后变为高电平。 但这不是 always..it 是间歇性的。

这意味着、每10次我们就会看到 FPGA 变为低电平...其他次也没有问题。

因此、Xilinx FPGA 支持团队建议检查电源。

想知道 TPS564242输出是否是个问题。

请告诉我要设置 VEN1电压、以便在使能为0v 时输出为0v、在使能为高电平时输出为1.8V。

由于 VEN 导通和关断重叠、因此其阈值电平令人困惑。

还有一点、在之前的原型中、我们使用以下 IC 来提供 SoC 和 FPGA 电源。 当时 FPGA 运转良好。 但当我更改为 TPS564242作为 SoC 和 FPGA 的单独电源时、我们也看到了问题。

我们是否可以通过电子邮件联系、讨论此问题。 因为我们制造的电路板不多、并且在所有电路板中都可以观察到该问题。 因此、我们需要尽快解决此问题、以便满足向客户交付电路板的时间表。

谢谢!

此致、

Sumathi