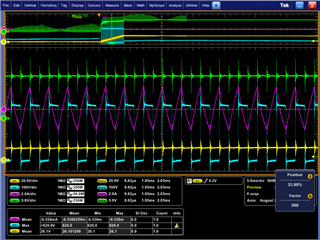

Thread 中讨论的其他器件: PMP40580、 TL431

工具与软件:

前一个线程已锁定、因此我无法添加到其中、但我只尝试为 LLC 供电就意识到了错误。 我没想到能够通过 VDD 引脚的外部电源来启动芯片、因为我认为必须通过 HV 引脚在内部充电、所以这个回答对我很有帮助。

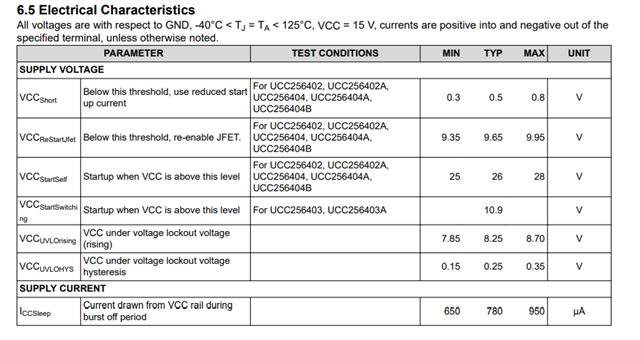

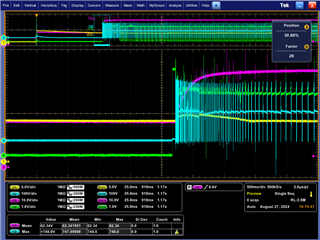

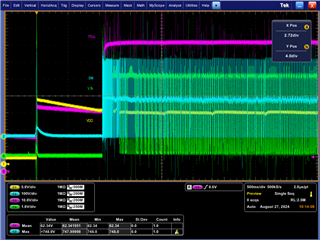

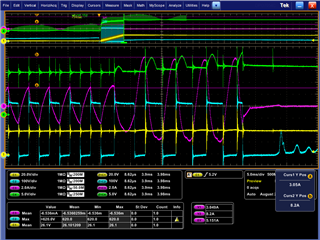

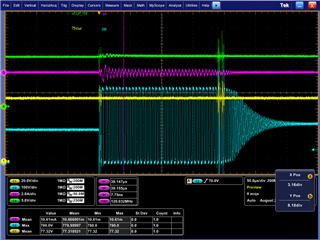

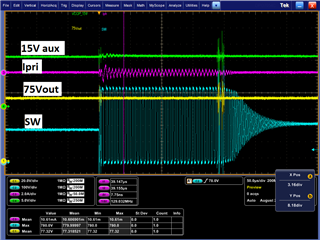

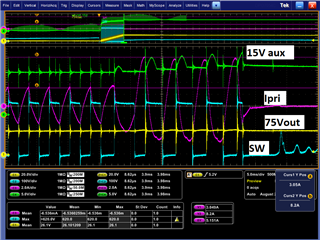

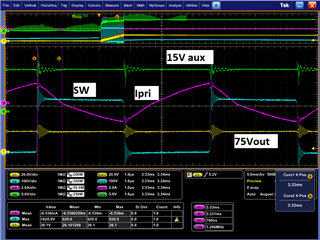

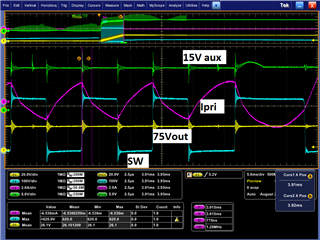

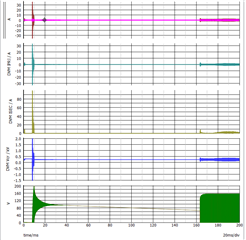

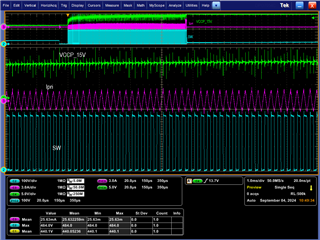

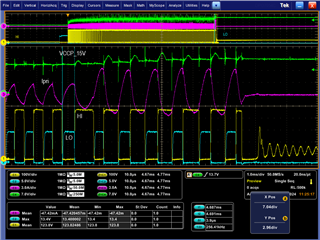

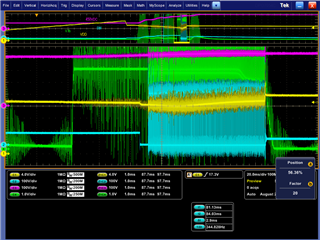

不过、我现在要谈谈启动时可能出现的故障。 我已经附上了几个示波器图、我的原理图、我使用的变压器数据表、我的 Excel 设计表以及我的设计的 simplis 模型作为参考。 我认为、simplis 模型的优点是模拟了我在工作台上的测量结果、但我不确定从哪里开始寻找问题。 我最大的问题是我是否正确地对变压器建模、但我认为我的设计中的所有值都与我从设计电子表格中获得的值相匹配。 示波器图显示了450V 输入、VDD 引脚、FB 引脚和开关节点 SW。

LLC 设计的一般规格-

输入电压为450VDC;输出电压为75VDC;输出电流最大值为2.667A。

UCC256404启动开关、然后在大约5ms 后停止、这也是仿真的功能、但仿真会在大约30ms 后重新启动、而我的 PCB 没有。 我将其归因于某些未实现的故障模式。 LLC 的输出(未在示波器图中显示)应调节至75V、但在器件关闭之前、它只能达到约40-45V、这也与仿真相同。

如果能够浏览我的设计表和/或原理图、看看我是否做得有误、或者对在 哪里寻找问题有一些想法、我将不胜感激。 我对 LLC 设计和 SIMPLIS 都不熟悉、因此我肯定要学习其中的内容。

谢谢!

Joe

e2e.ti.com/.../UCC25640x-Design-Calculator-Rev4-take2.xlsx

e2e.ti.com/.../LLC-Transformer.pdfe2e.ti.com/.../3630.n10812F_2D00_0_5F00_Schematic_5F00_Aug5_5F00_2024.pdfe2e.ti.com/.../UCC25640x-Simulation-Test-Bench-ERGdesign.zip