工具与软件:

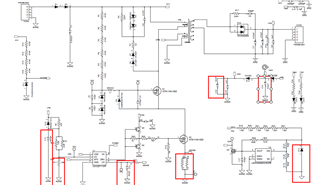

您好! 我已经根据文档创建了 SMPS "用于电机驱动器的400V 到690V 交流输入50W 隔离式反激电源参考设计"。

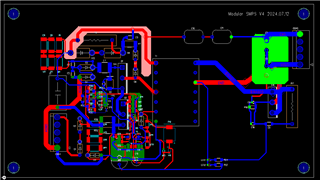

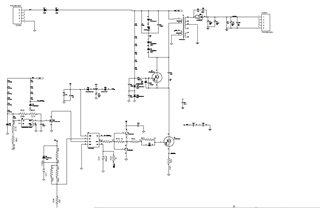

原理图如下、PCB 布局以相同的方式完成。

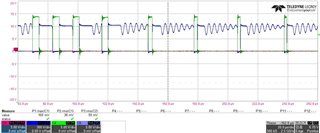

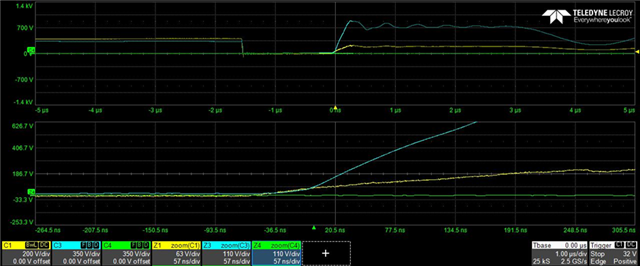

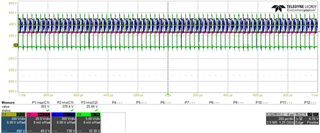

我按照指南创建它、我目前正在测试它。 到目前为止、我已确认在600Vdc 输入下输出为1A (请参阅图1和2)。 然而、我有一些问题、因此我无法在实验中进一步升高电压。

-

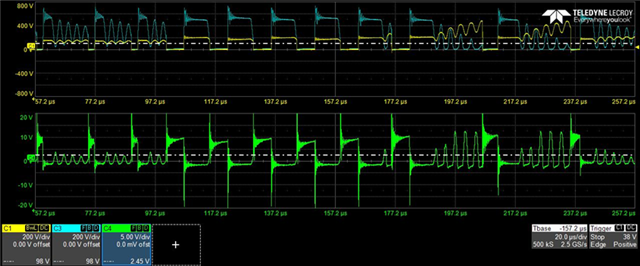

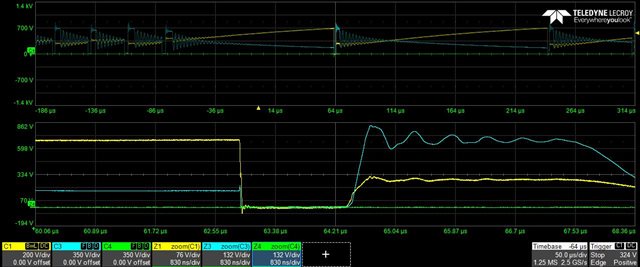

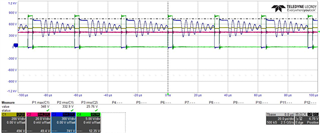

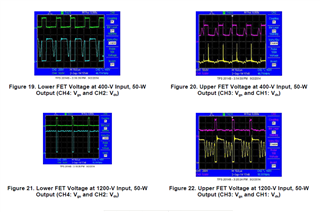

本文档说明了以下情况:在较低电压下(当上部开关齐纳二极管 V < Vin 时)、图19显示了 VDS 中没有振铃。 但在我的实验波形中、我可以看到振铃(请参阅图3)。

-

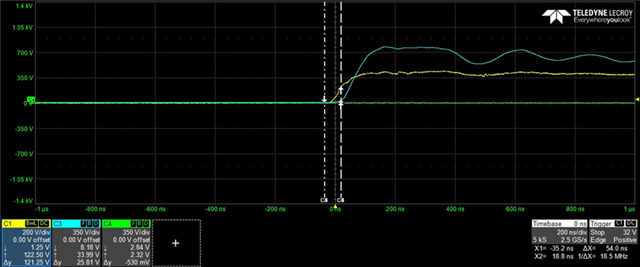

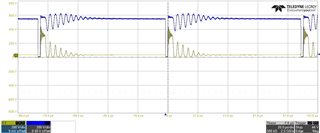

按照该指南设计的 SMPS 开始在400Vdc 输入下工作、这也发生在我的实验中。 但是、当我连接示波器的无源探头来测量上部开关的 Vgs 时、电路在300Vdc 输入下运行、而不应该这样做。 这种异常运行是否可能是由于示波器无源探头中存在电容造成的? (请参见图4和图5)

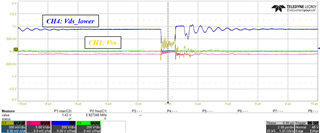

(CH1:D13V、CH2:Vout、CH3:下部 FET Vds、CH4:上部 FET Vgs // Vin:290Vdc) -

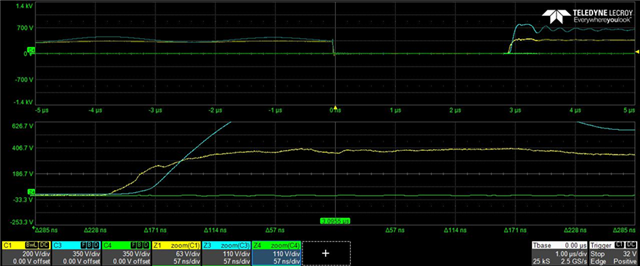

在 Nomarl 工作条件下、通过差分探头测量上开关 Vgs、测试图如图5所示。 在下部开关关闭时、似乎已经关闭 on.because、上部开关 Vgs 为5~6V。 我想它是否在衡量错误。 并且我预计 Vgs 会上升到12V、因为并联齐纳二极管的额定电压为12V。但是、它仅达到78V。(当然、我还在指南文档中确认 Vgs 仅达到78V。)

-

鉴于下部 FET 上的振铃以及从第2点和第3点观察到的情况、上部 FET 是否始终导通?

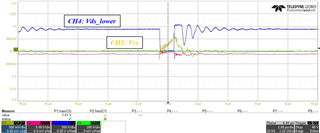

图1 (CH1:D13V、CH2:Vout、CH3:LOWER FET Vds、CH4:LOWER FET Vgs // Vin:500Vdc)

图2.

(CH1:D13V、CH2:Vout、CH3:下部 FET Vds、CH4: 下部 FET Vgs // Vin: 500Vdc)

图3 (CH1:D13V、CH2:Vout、CH3:LOWER FET Vds、CH4:LOWER FET Vgs // Vin: 500Vdc)

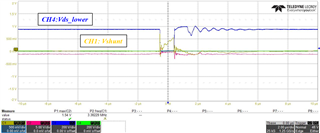

图4 CH1:D13V、CH2:Vout、CH3:LOWER FET Vds、CH4:LOWER FET Vgs // Vin:290Vdc)

图5 CH1:D13V、CH2:Vout、CH3:LOWER FET Vds、CH4:LOWER FET Vgs // Vin:290Vdc)。

在正常情况下、较低的开关 Vds 低于。 有时它的剂量没有振铃、有时会有振铃。 我想这是为什么。