主题中讨论的其他器件: TPS631011、 TPS61033

工具与软件:

尊敬的 TI 团队:

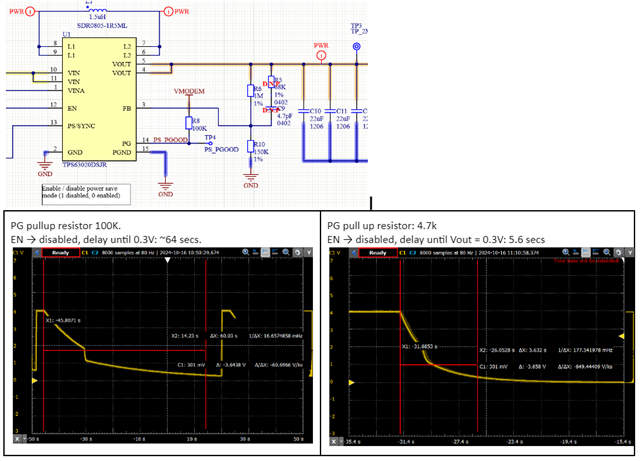

我们 计划为 TPS63020.*使用电源正常引脚实现输出放电功能

您能否说明最大电流能力是多少? 我们 在数据表中找不到该信息。

感谢您的支持。

Fabio Leitao

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tao、

听起来不错。

感谢您的澄清。

因此、 当转换器被禁用(EN =低电平)时、电源正常状态最终会被拉至低电平。

可以粗略估算一下如何计算放电时间(仅考虑电源正常引脚路径)

T =(R_pg + R_ON_MOSFET)* Cout * log (1/r)、 其中:

- R_pg 是上拉电阻器、

- R_ON_MOSFET 可以在4K-40k 之间变化(最 慢放电时间的最坏情况为40k)

- Cout 输出电容、

- r 的放电端子电压比

谢谢!

Fabio

您好、Tao、

感谢您的留言。

对于不同的上拉电阻值、当 EN 设置为低电平时、我已执行了以下测量。

在放电期间、总输出电容约为~250uF。

可以看出、改变电源正常引脚上的上拉电阻器会产生不同的放电延迟。

例如、当使用4.7k 上拉电阻时、虽然我们的预期值只是稍低一些、但我们的测量值大约为5.6s。 这 可能是由您提到的 N-FET 的内阻(4K-40k?)导致的。

我们只想 了解 考虑到该内部电阻、延迟增加的最坏情况是什么。

感谢您的支持。

-是的, 当器件被禁用时 PG 被拉低。

[报价 userid="486697" url="~/support/power-management-group/power-management/f/power-management-forum/1425707/tps63020-output-discharge---current-capability-for-pg-pin/5467301 #5467301"]否、禁用器件时、FET 内部关闭。 因此、恐怕我们无法使用此引脚进行放电。因此、当我们禁用电路时、这确实可以用于使输出电路放电。

-是的,输入电压恒定为5.1V。 仅 EN 引脚被切换。

我认为这很清楚。 这仅仅意味着对于最坏的情况 、我们 必须考虑40k 的最慢放电时间。

感谢您的支持、

Fabio