工具与软件:

你(们)好

我想知道您是否认为这款器件适合我在托盘中执行的操作。 下面是规格

PCB 尺寸: 28mm x 30mm

PCB 是一个4层电路板

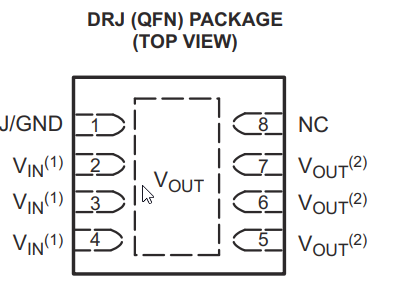

器件: TLV117-50CDRJR (QDFN)

VIN = 15

VOUT = 5V

输出电流= 150mA (最大值)

热结空气= 38.2

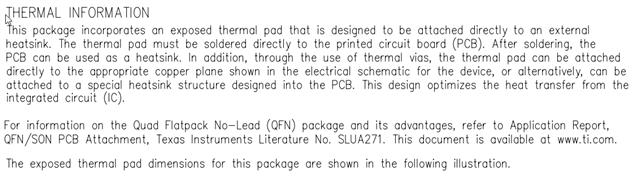

T =(15-5)* 0.15 * 38.2 = 82.45°C

82.45低于125°C 的最高温度。

您是否建议使用此器件、或者您是否有具有较低结温的替代器件、或者您是否建议使用开关稳压器。

谢谢