Other Parts Discussed in Thread: LM5060

工具与软件:

Dears、

我的客户端在控制器项目中使用了 LM5060。 OVP 保护点设置为49V。 在测试过程中发现、当触发 OVP 时、MOS 栅极端的电压将加载80mA、导致 G END 直接下降至0。 然而、由于在 MOS 源端存在电容、电压缓慢下降、导致 MOS Vgs 之间的负电压超过限值和 MOS 损坏。

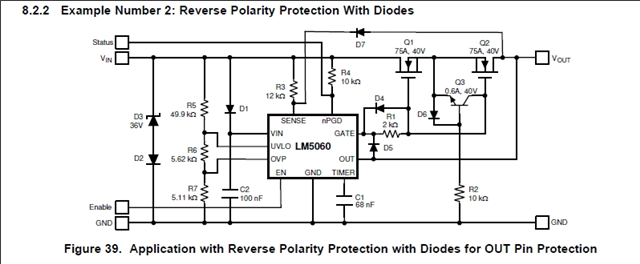

查看 LM5060数据表后、客户在 MOS GS 两端添加了一个二极管用于电流放电。 如下图和随附的 PDF 电路图所示。

目前的问题如下:

在此状态下触发 OVP 时、电容器后端的能量将由 LM5060的80mA 内部负载消耗。 此时、LM5060需要承受4W 的最大功耗和约15ms 的2W 的平均功耗。 由于 LM5060的热阻为 LM5060/W、请确认162.1℃ 是否能够承受这一瞬时功耗、以及它是否会导致过热或其他故障? 如果无法承受、TI 是否针对该器件的后端电容器推荐了任何其他放电电路?

2.客户增加了一个肖特基二极管后、在高温情况下二极管漏电流太大、导致 MOS 无法正常驱动、后端断电。 在60°C 条件下的实际测试中、肖特基二极管漏电流为18uA、接近于 LM5060栅极引脚的驱动能力。 您能否确认数据表中是否有二极管 D5的推荐规格模型?

e2e.ti.com/.../LM5060_3575EF8DFE56_.zip

请参阅随附的原理图

非常感谢

Arabella