工具与软件:

您好!

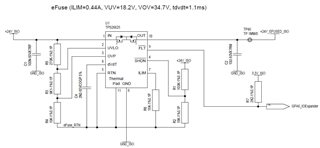

我们 在其中一个设计中使用了 TPS26625电子保险丝。

原理图如下所示:

我们在其中一个功能测试程序中检查输出电压、同时将输入电压设置为低于 UVLO 限制。 则电子保险丝需要保持关闭状态。

输出在此测试步骤中未加载、不进入任何其他电路(仅连接器)。

输入电压介于18V 和19V 之间时、电子保险丝的标称导通电压。

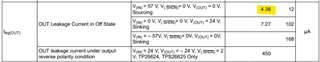

在第一批中、将输入电压设置为17.5V 时、输出电压始终约为0.65V (测试限制为0.75V)。

现在我们有一批新的批次、其中输出电压大约为3V、而不是低于0.75V。

电子保险丝处于欠压锁定状态时、输出电压是否可能上升到如此高的电平?

此致、

Patrick