Thread 中讨论的其他器件:LM5155、、 TPS61175.

工具与软件:

您好!

我发现 LM5156的数据表未清楚定义如何实现脉冲跳跃。 其他相关的论坛问题似乎表明实现类似于其他 IC 系列、例如 LM5155和 APT61776等

我已找到应用报告 SLVA353 - 2009年7月。 本文详细介绍了此类脉冲跳跃机制。 LM5156是否使用相同的技术?

提前感谢

Aidan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我发现 LM5156的数据表未清楚定义如何实现脉冲跳跃。 其他相关的论坛问题似乎表明实现类似于其他 IC 系列、例如 LM5155和 APT61776等

我已找到应用报告 SLVA353 - 2009年7月。 本文详细介绍了此类脉冲跳跃机制。 LM5156是否使用相同的技术?

提前感谢

Aidan

尊敬的 Aidan:

脉冲跳跃与器件的最短导通时间能力有关。

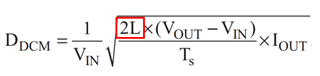

在轻负载条件下、器件将尽可能长时间保持固定频率的一致 PWM 信号、但如果占空比变得如此小、以至于 MOSFET 所需的导通时间将小于器件的导通时间限制、它将开始脉冲跳跃以避免输出电压失控。

脉冲跳跃模式的入口点可通过电感进行调节。 较大的电感将增加 DCM 运行模式下的占空比、从而增加器件的导通时间。

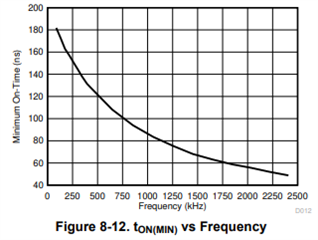

对于 LM5156、最小导通时间能力遵循开关频率。 因此、更改 fsw 将不会影响器件的脉冲跳跃行为。

如果有其他问题、敬请告知。

此致、

Niklas

尊敬的 Niklas:

实际上、这是非常有用的、感谢您指出此图表、数据表文本说明中实际上并未引用此图表、因此不清楚这种关系是否存在。 它特别在峰值电流方面非常重要。 如果您能弄清楚在 IC 中实现这一点的确切机制、会很有帮助。 如果我正确理解这一点、如您所述、我将感谢您的确认;最短导通时间与频率相关、在选通期间、无论 PWM 复位触发器的状态如何、还是电流限制复位触发器如何、都将遵守该最短导通时间? 这样、如果我们有一个非常大的前沿尖峰或电感器尺寸过小或饱和、那么在这个短时间内很可能有非常大的电流流入 FET。

您是否能够确认 LM5156是否使用了与我最初引用的应用手册中所述相同的内部逻辑来生成脉冲跳跃过程、您是否还可以确认(因为即使在应用手册中也没有清除)、以便在最短导通时间内忽略电流限制复位触发条件。 也就是说、一旦栅极 引脚被驱动为高电平、它将在最短导通时间内保持高电平、无论系统中是否存在任何其他明显的信号、包括电流限制比较器?

期待进一步的反馈。

祝你一切顺利

Aidan

尊敬的 Aidan:

[报价 userid="632841" url="~/support/power-management-group/power-management/f/power-management-forum/1448811/lm5156-pulse-skipping-implementation-details/5563747 #5563747"]正如您所说、最短接通时间与频率有关、并且在选通期间、无论 PWM 复位触发器的状态如何、或者实际上是电流限制复位触发器如何、都将遵守此最短接通时间?是的、这是正确的。 即使在最短导通时间内触发过流保护、驱动器电压仍将保持高电平、直到达到最短导通时间、然后关断。

在每个周期的开始还有一个额外的消隐时间、无法触发 OCP。 这完全是为了滤除由于 FET 导通而产生的浪涌电流。

通读您参考的应用手册、我不确定实施是否与 LM5156相同、因为我不知道 TPS61175器件。

对于 LM5156、该机制还包括 FB 处的电压。 该器件以最短导通时间进行开关、直到 Vout 上升到 OVP 阈值。 然后、器件将停止运行(进入脉冲跳跃模式)、仅在 FB 下降时发送脉冲。

此致、

Niklas

事实上、我之前的问题是、IC 如何准确检测到 FB 接地、我觉得没有非常有效地回答这个问题。 因为你是如此乐于助人,我想再试一次。 数据表显示、当 FB 接地时"反激式"、COMP 最小电压钳位将被禁用。 如果 IC 似乎没有以某种方式进行测量、那么它如何知道 FB 接地?

LM5156:FB 引脚连接至 GND 以实现反激式模式的检测-电源管理论坛-电源管理- TI E2E 支持论坛

还有更多见解吗?

一切都是这样

Aidan

尊敬的 Aidan:

感谢您的反馈。

消隐时间为~50ns。

在 FB 接地的反激式拓扑中、跳跃模式机制不起作用。

占空比通过 COMP 引脚调节定义。 然而、即使 COMP 下降至0V、器件也将以最小占空比保持运行。 这是因为 FB 永远不会触发过压、因为它接地。 因此、器件不会停止开关。

因此、建议在反激式拓扑中的 Vout 上放置一个钳位二极管、以避免 Vout 在零负载条件下失控。

此致、

Niklas