请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS552872 工具与软件:

我已经构建了一个原型板、其中 TPS552872RYQR 设置为3V 输出电压。 从功能上讲、该设计按照应用的预期工作、但我注意到、与数据表规格相比、观察到的 VOUT 漏电流有一个奇特的不匹配现象。

数据表列出了禁用器件时 VOUT 漏电流典型值为1uA、最大值为20uA。 但是、我的测量值明显大于该值-大约160uA。

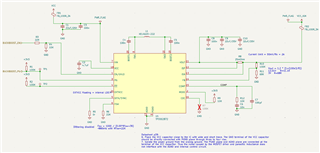

此器件的原理图:

我将在 VCC 上施加8V 电压、并已移除 FB2进行测试、以确保泄漏来自 U1而不是电路的其余部分。

当 BUCKBOOST_EN 悬空或逻辑0时、VOUT 上的电压测量值为4V。 当我添加1k 的接地电阻(在反馈路径之后)时、输出电压降至~160mV。

我还尝试了在不存在+3v3电源轨的情况下运行 IC (以通过逻辑引脚上的内部保护二极管排除潜在的泄漏路径)、这并没有改变观察到的泄漏。

我有一个问题:是否还有我遗漏的其他 VOUT 泄漏路径? 观察到的行为是否是预期行为?