工具与软件:

您好!

我们使用 UCC21750已有很长一段时间了、没有任何问题。 我们最近在同步整流器电路中使用了它。 首先、我们禁用了由驱动器芯片驱动的 MOSFET、但我们仍然看到 FLT 引脚变为低电平。 这很奇怪、因为 PWM 始终为低电平。

有没有任何其他原因导致即使 PWM 始终为低电平、FLT 也会变为低电平?

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、Sasikala、

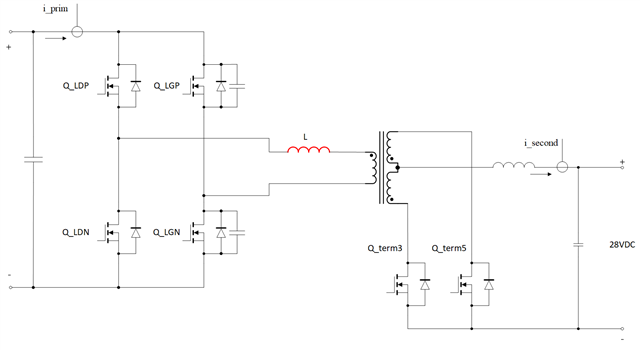

两个 MOSFET (Q_term3和 Q_term5)用于相移全桥直流/直流转换器的次级侧。 首先、我们尝试使用两个 MOSFET 作为二极管。 因此、驱动器甚至不应该工作、更不用说报告故障了。

谢谢。

感谢您的快速响应。 非常感谢。

请务必分享这些波形、这将有助于我们了解 系统场景。 如果采集的通道数超过4个。 我们希望监控接近栅极驱动器的输出电压、VDD 电压。

您提到1个驱动器的 FLT 引脚为低电平。 (哪个 MOSFET 驱动器位置?) 是否可以将栅极驱动器替换为另一个驱动器以了解其是否是特定的一个驱动器故障、或者安装在该位置的任何驱动器的行为是否可重复? 尝试了解其驱动器是否存在故障或 在特定驾驶员位置是否观察到 FLT。

谢谢

SASI

Charlie、您好!

除非将该器件更换为其他器件、否则我们不知道它是否是特定器件问题。 还是在同一位置的多个电路板上观察到故障?

是仅当触发 DESAT 时才会触发 FLT。 造成 FLT 出现错误的潜在原因是系统噪声导致 DESAT >阈值或其他影响 FLT 的方式、我们需要通过观察波形来了解这一点。

FLT、VCC、VDD、DESAT、RDY、 OUTH、OUTL。 (请使用 高 BW 探头、以便捕获高频分量)对于所有次级信号捕获、它需要采用差分探头。

期待您的拍摄。

谢谢

SASI

大家好、Sasi、

很抱歉这么晚才回复。

DESAT 引脚实际上直接链接到 COM 以禁用 DESAT 保护。 但是、当我们进行测试阶跃负载时、仍然会触发 DESAT 故障。

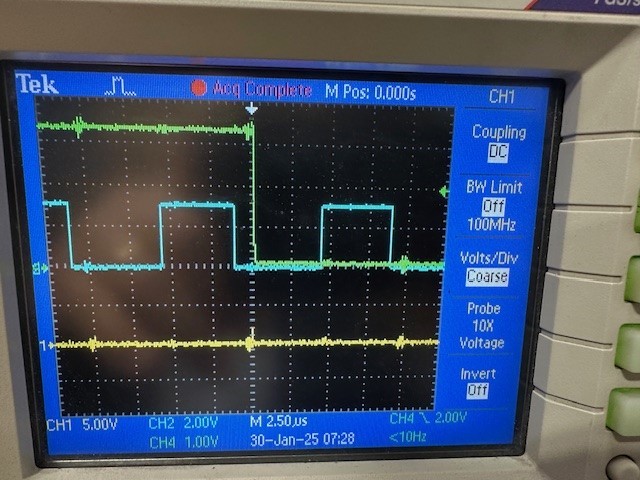

我截取了 Vin+到 Vin-、DESAT 和 FLT 的屏幕截图、如下所示。 示波器的探针带宽为200MHz 和100MHz。

CH1 (黄色曲线)是 DESAT 信号、CH2 (蓝色曲线)是 PWM 输入信号、而 CH4 (绿色曲线)是 FLT 信号。 此时 FLT 降至零、PWM 输入为低电平、DESAT 也为低电平。 DESAT 信号的噪声峰值约为2.2V、远低于9V 阈值。 但 FLT 被拉至低电平以报告故障。

按照您的建议、我将检查 VCC、VDD、VOUTH 和 VOUTL 的波形。

谢谢。

下面的屏幕截图中显示了 VCC (Ch2蓝色曲线)、VOUT (Ch1、黄色曲线)和 FLT (Ch4、绿色曲线)的波形。 当发生 FLT 时、VOUT 为低电平、VCC 为3.3V)。

下面的屏幕截图中显示了 VDD (Ch2蓝色曲线)、VOUT (Ch1、黄色曲线)和 FLT (Ch4、绿色曲线)的波形。 当 FLT 发生时、VOUT 为低电平、而 VDD 为15V。

所有示例都显示不应生成和报告去饱和故障。 请在此处帮助找到可能的故障生成机制、并提供可能的解决方案建议。

谢谢。

在该论坛的另一篇文章 UCC21750-Q1:DESAT 错误-电源管理论坛-电源管理- TI E2E 支持论坛中、Andy Robles 提到、如果 DESAT 引脚被连接到 COM 引脚、而 FLT 仍被拉至低电平、则应存在 系统噪声耦合到栅极驱动器内部电路中。

这正是我们的情况。

问题是:系统噪声耦合到芯片内部电路的路径是什么、如何将其切断以确保不报告错误的 FLT 且不会将芯片锁定?

Charlie、您好!

感谢所有屏幕截图和排除所有潜在的 FLT 低情景。

在以下情况下、FLT 将很低:发生 DESAT、VCC /GND 电源受到干扰、噪声 影响 VDD 平面。

如果是噪声引起的、则需要隔离噪声源。 我们对噪声耦合路径的了解主要通过 COM 和 VEE 实现、有些情况下还通过 GATE (OUH/OUTL)

在 FLT 事件期间、我可以看到噪声耦合到所有通道(假设是由某些开关导致的)。

请尝试以下选项、优先级如下列表所示。

为了减少电源噪声耦合:

1.添加共模扼流圈到电源 VDD、VEE

2.根据系统噪声范围、还要确保10nF 电容(和/或)的其他较小值

为了减少接地噪声耦合:

是否有办法使噪声源远离栅极驱动器? 是 VEE 有噪声节点与栅极驱动器 COM/COM 平面之间共享的接地(作为1个大平面)、如果是、是否可以 将其分离。

2.是否可以减慢开关事件(通过使用缓冲电路)

是否可以在 GND 和 COM 节点之间添加 HV 电容器(~20pF)(这可以绕过共模 HF 噪声)

4.降低 GND 和 COM 之间的电容(由于隔离偏压)

为了减少栅极噪声耦合:

在栅极添加铁氧体磁珠(规划针对系统噪声范围的铁氧体磁珠频率)

希望它对您的情形有所帮助。 我现在将关闭 TT。 如需更多支持、我们可以通过电子邮件进行进一步沟通。

谢谢

SASI