工具与软件:

嗨、团队:

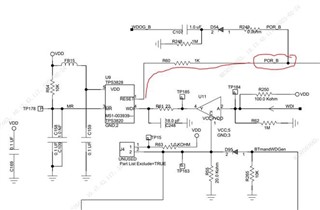

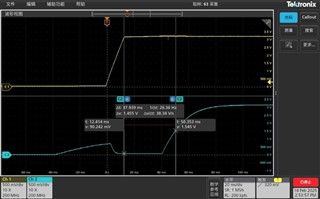

客户设计如下所示。 测试点位于 POR_B (红圈)。 在 VDD 上电期间、RESET 将产生干扰。 黄色波形为3.3V VDD。 蓝色波形是 POR_B (RESET 引脚)上的波形。 我想知道为什么会出现干扰以及如何消除干扰。 谢谢!

Rayna

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Rayna、 感谢您的问题!

您能否确认他们的电路板上是否有 FB15? VDD 引脚上似乎有一个电感器。 我想看看它的用途是什么。 则 TPS3820不需要该中断。

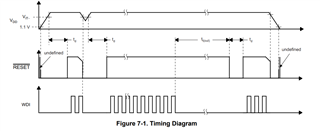

如果您查看上电的时序图、 VDD 会超过阈值 Vit、然后在 td 延迟后 RESET 变为高电平。 对于 TPS3820、td 延迟定义为典型值25ms。 这似乎是预期行为

如果您查看数据表、会发现 VPOR (上电复位)定义为0.4V;这意味着输出置为有效所需的最小功率为0.4V。 这就是 RESET 信号变为低电平的原因。 它几乎保持低电平25ms、然后再次使无效(变为高电平)。

但可以辨别 WDOG_B 信号有一些延迟。 请查看、当 VDD = 0V 时、复位已经缓慢增加。 由于它们具有1.0 μ F 的电容和1M Ω 的电阻、这会在 WDOG_B 上产生缓慢的事务 他们应该移除1.0uF 电容器、将其更改为较小的电容器。

Sila Atalar