工具与软件:

大家好!

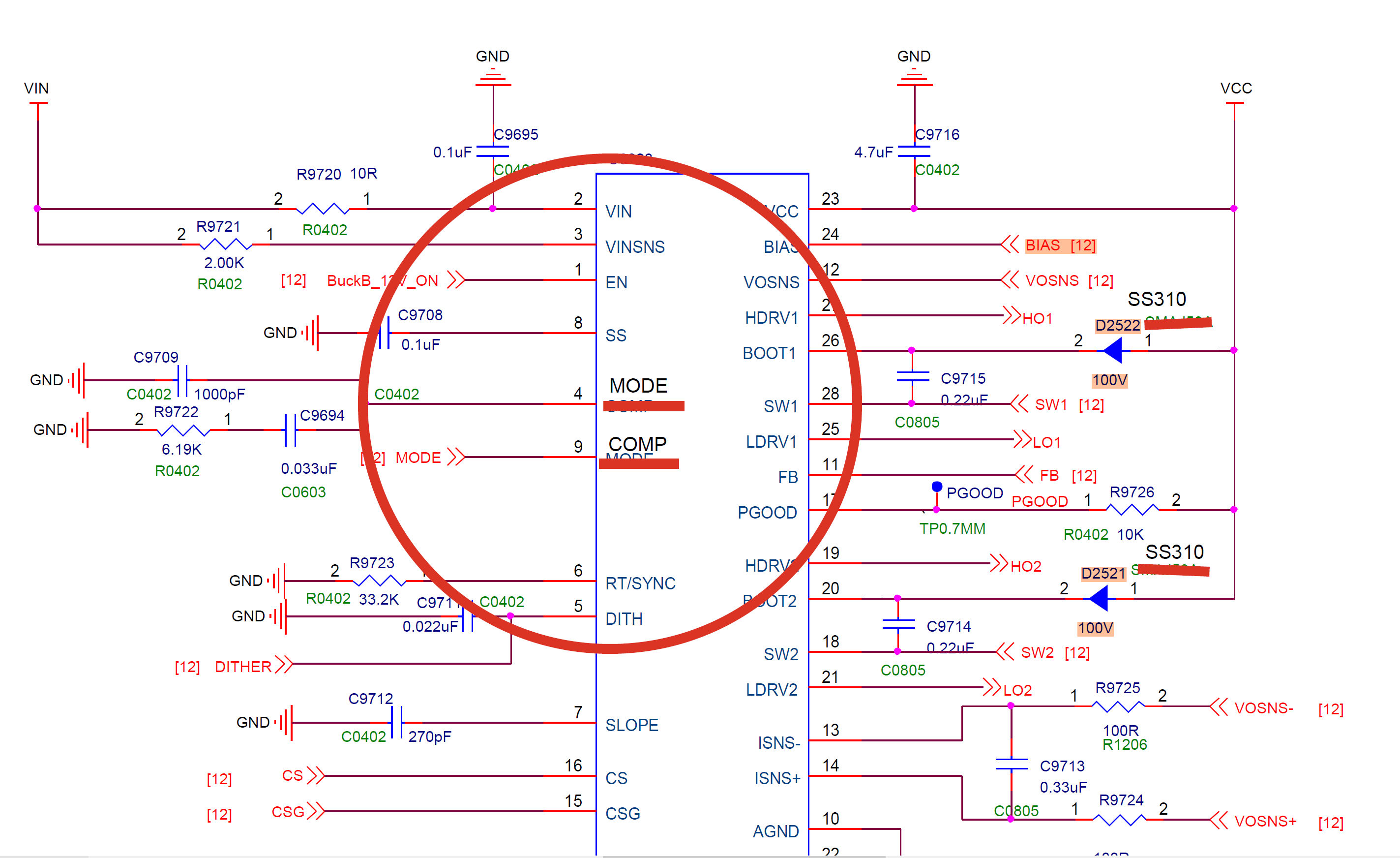

我们 将为路由器主板应用实施 LM5176。

基本规格为:

VIN = 8V-36

VOUT = 12V

Imax = 6A

我有第一个文章板、还有一个目前正在使用的其他板。 最初、我们遇到了启动问题以及在 Boost 模式下运行时遇到的问题。 Vin 引脚之前没有二极管、因此我通过将偏置反馈的输入设置为接地来禁用了偏置反馈。 这样解决了 BOOT 和低电压问题、并且我们似乎在所有条件下都具有良好的 Vcc。

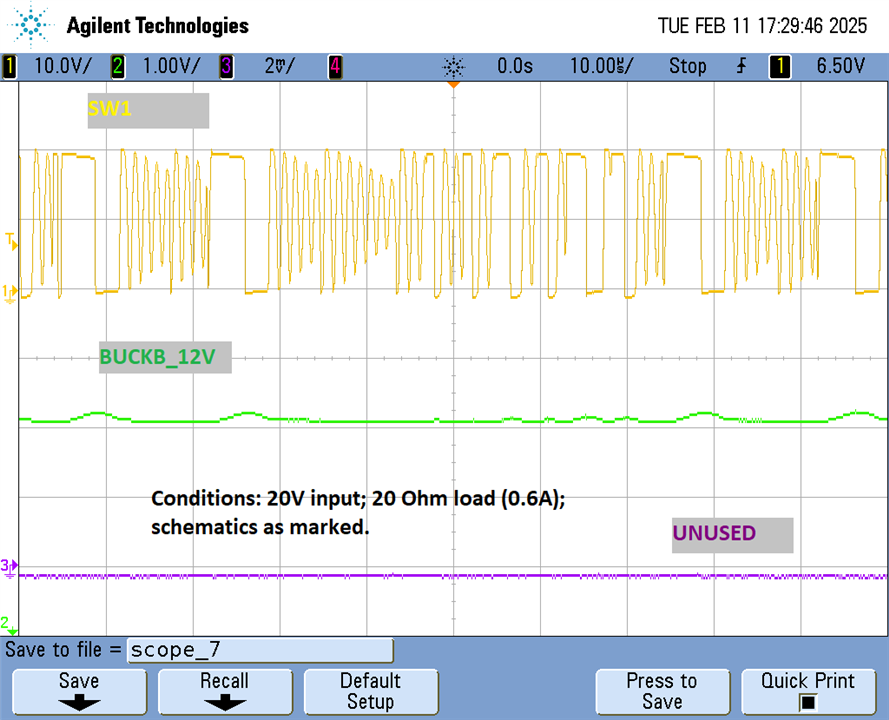

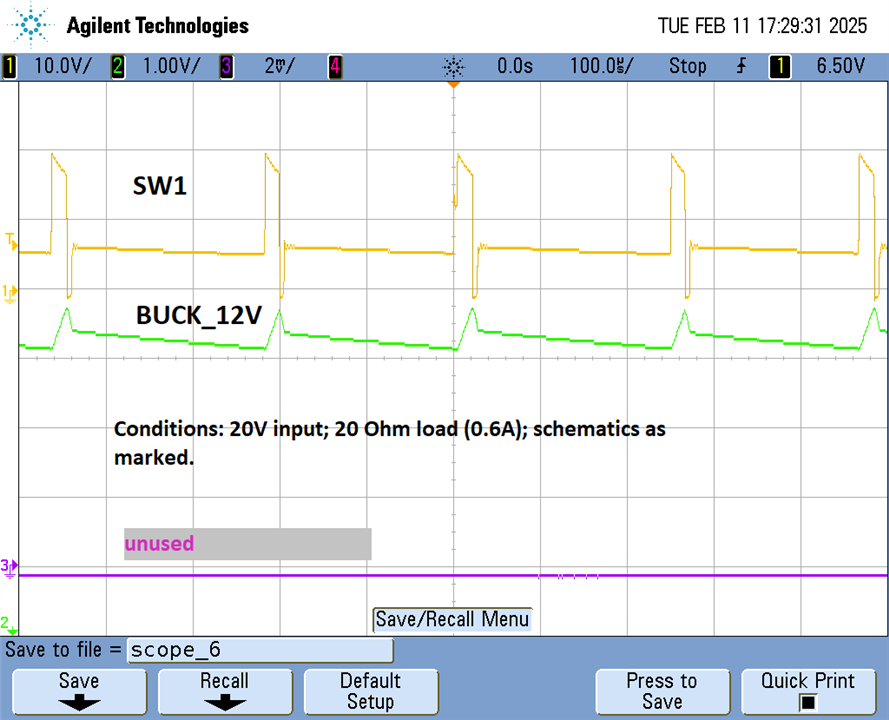

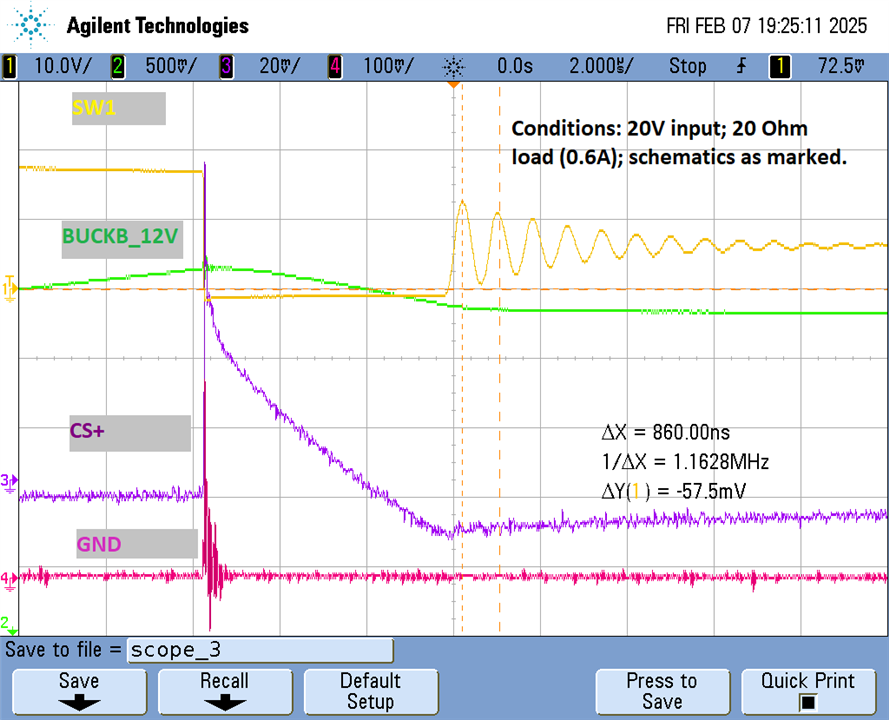

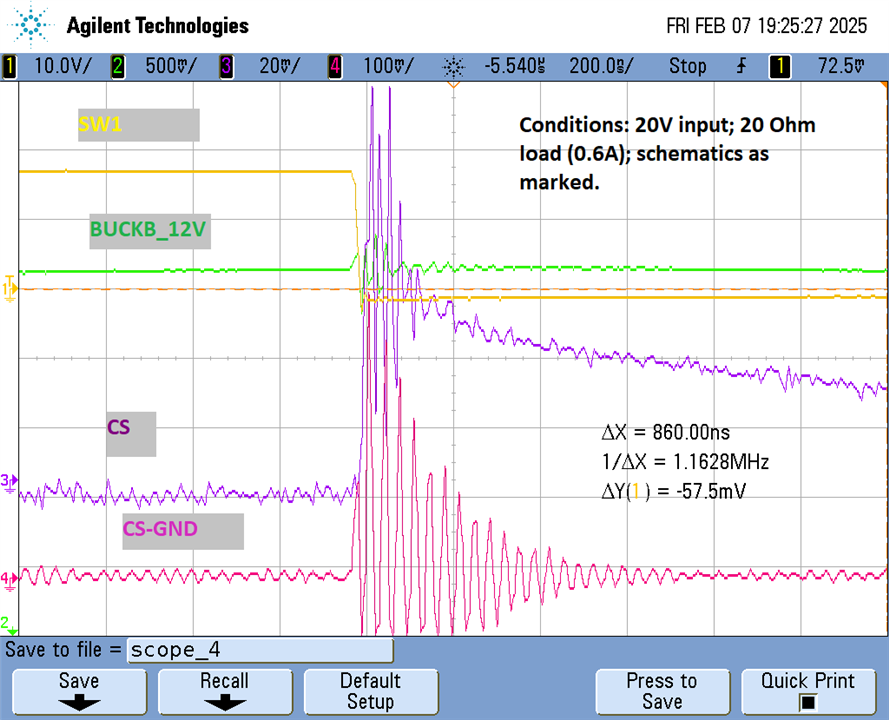

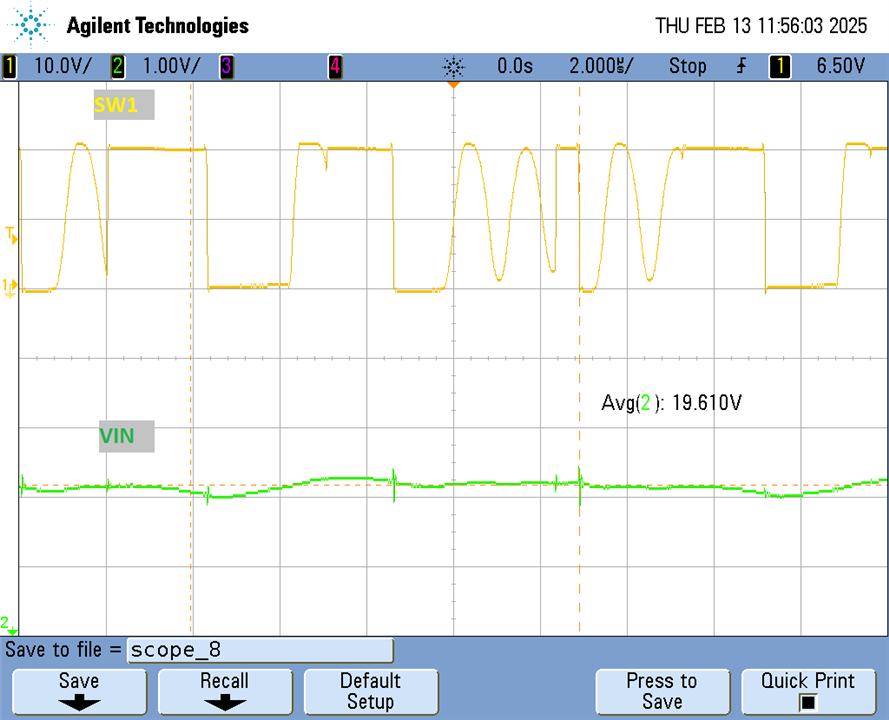

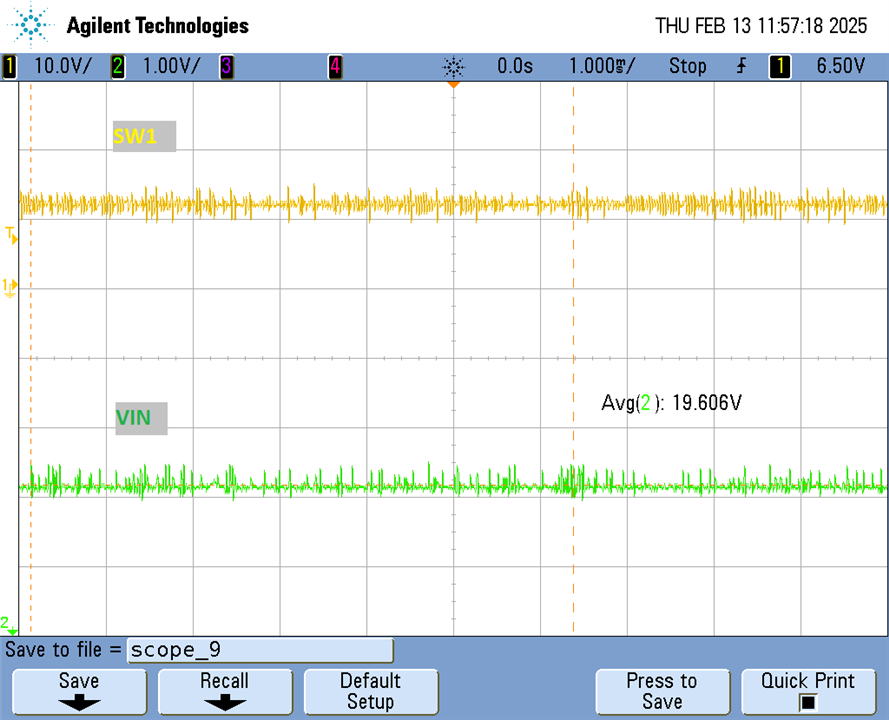

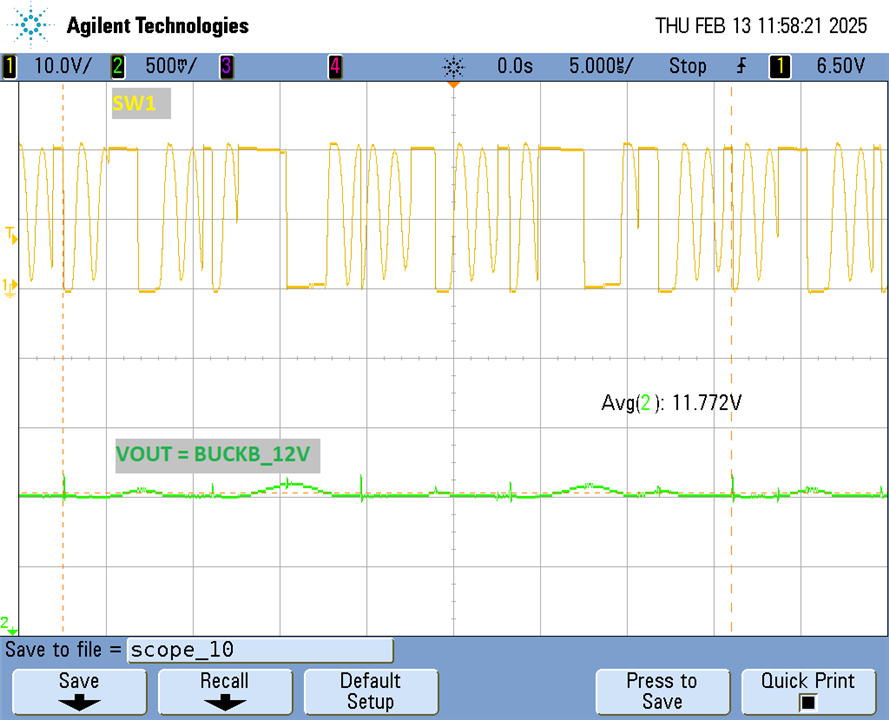

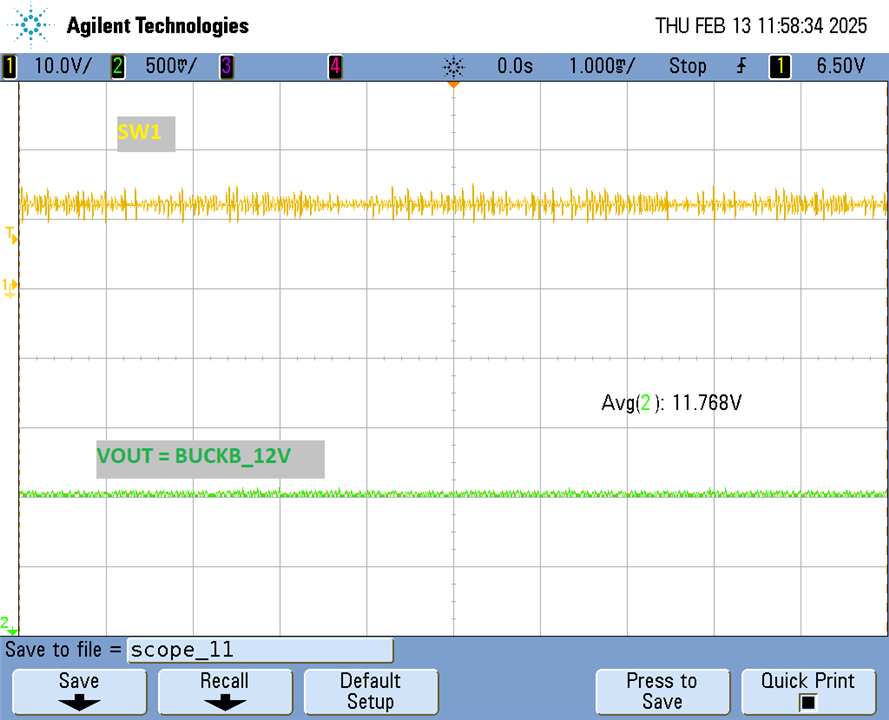

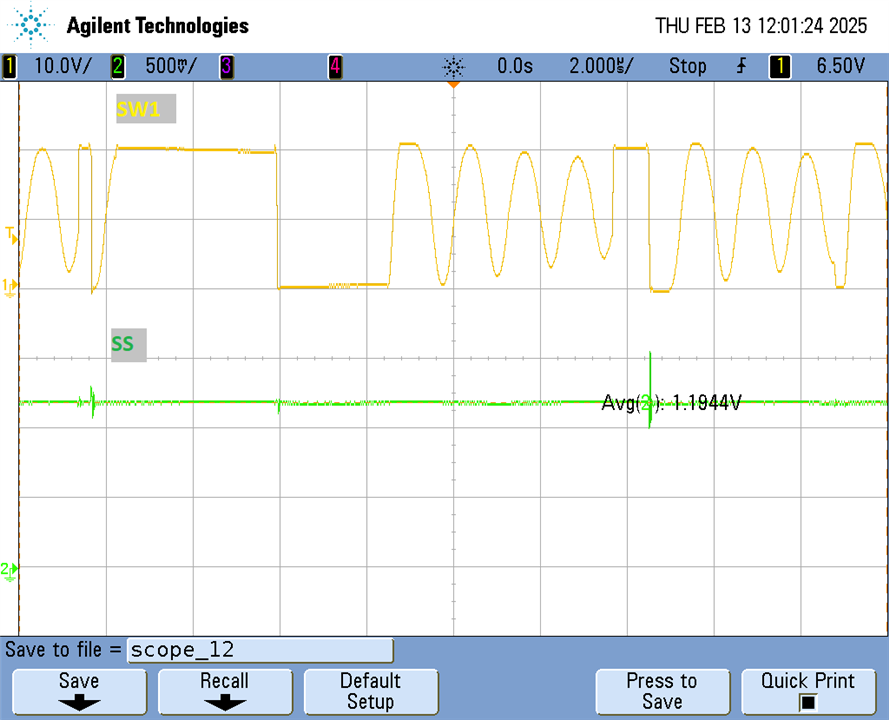

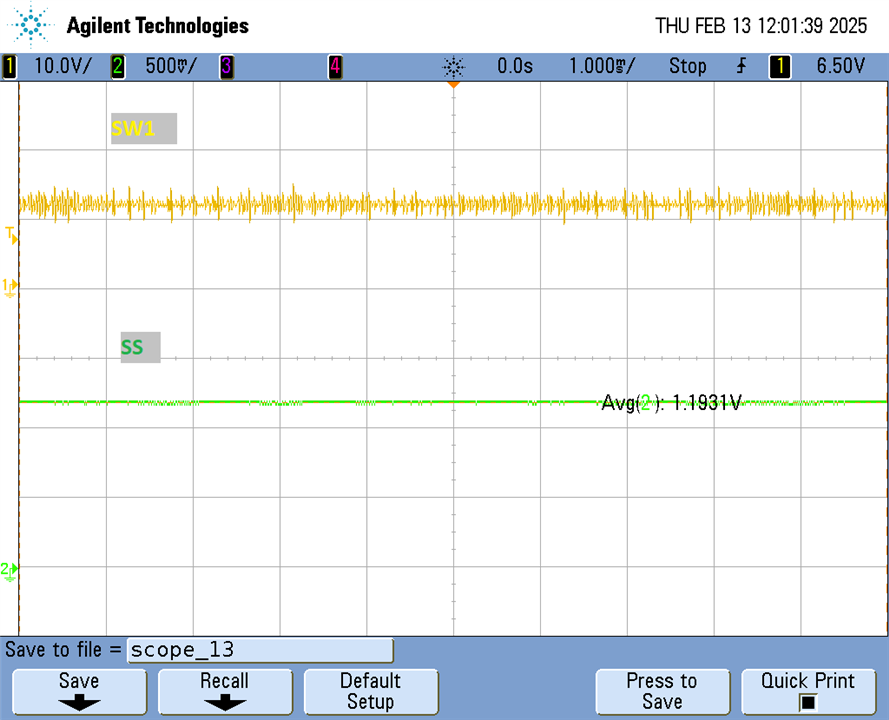

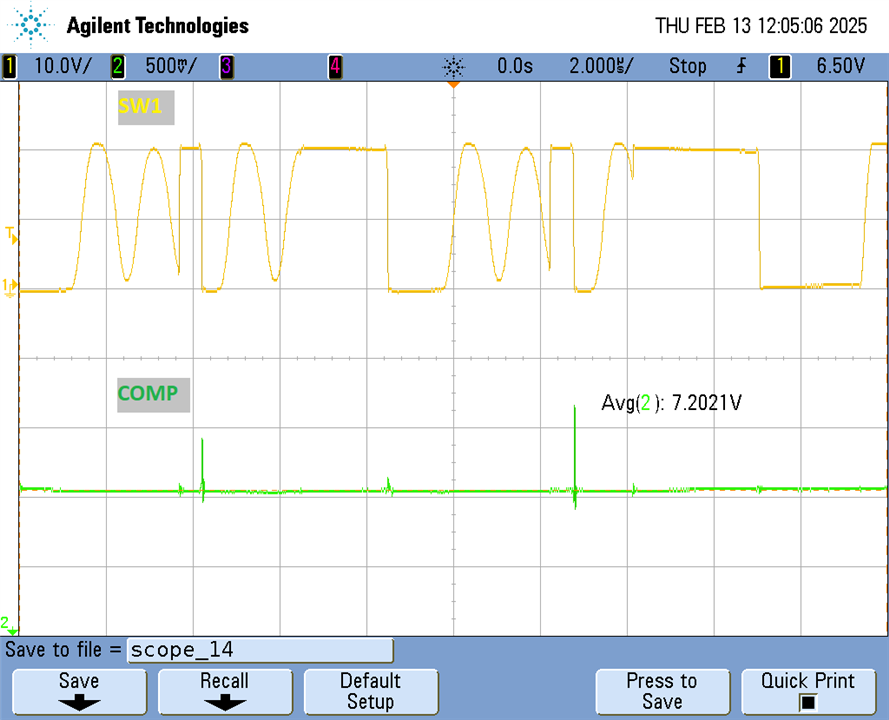

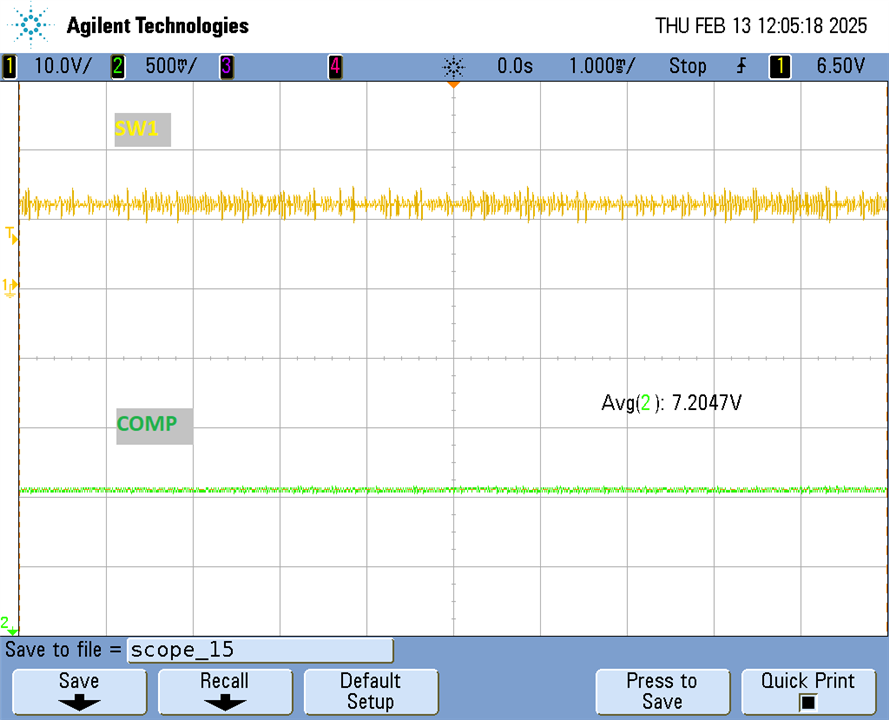

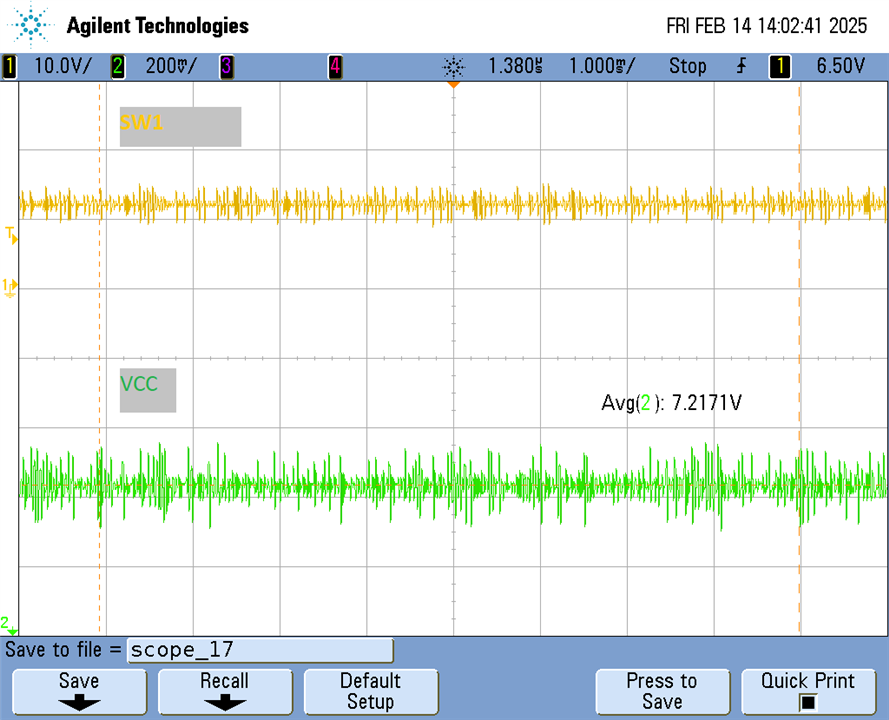

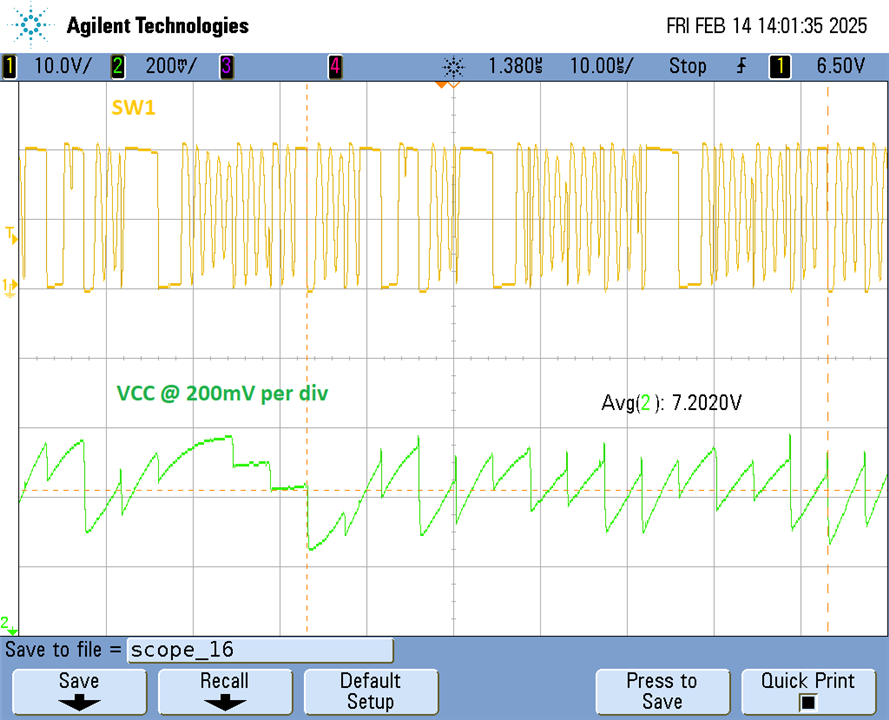

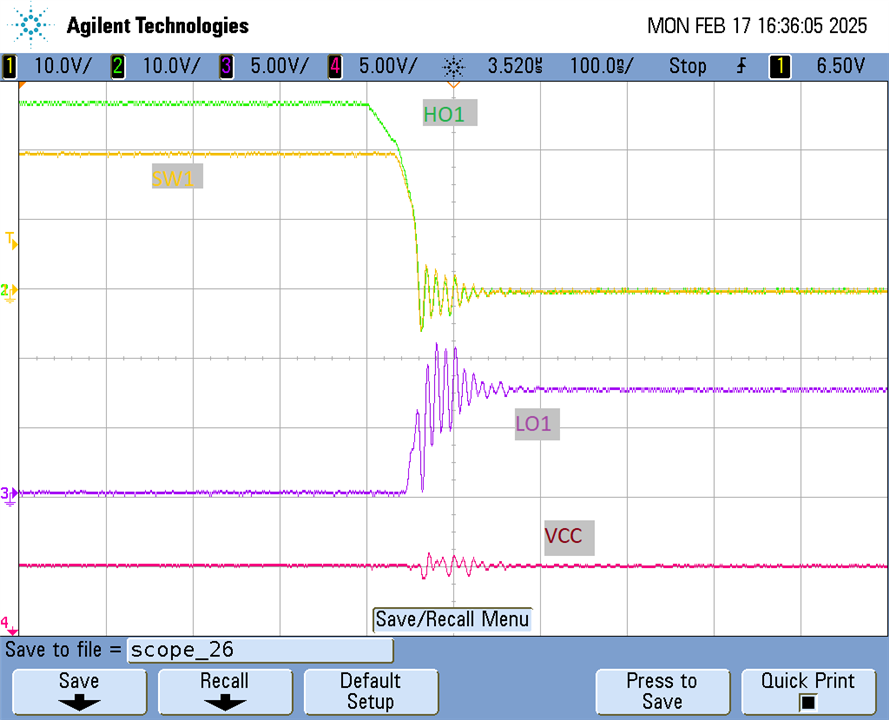

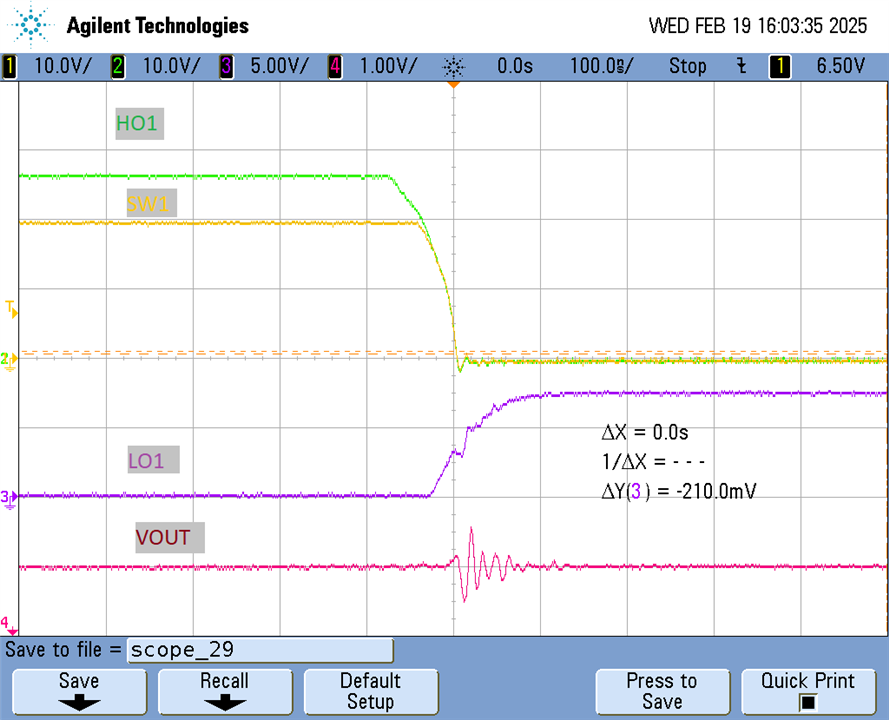

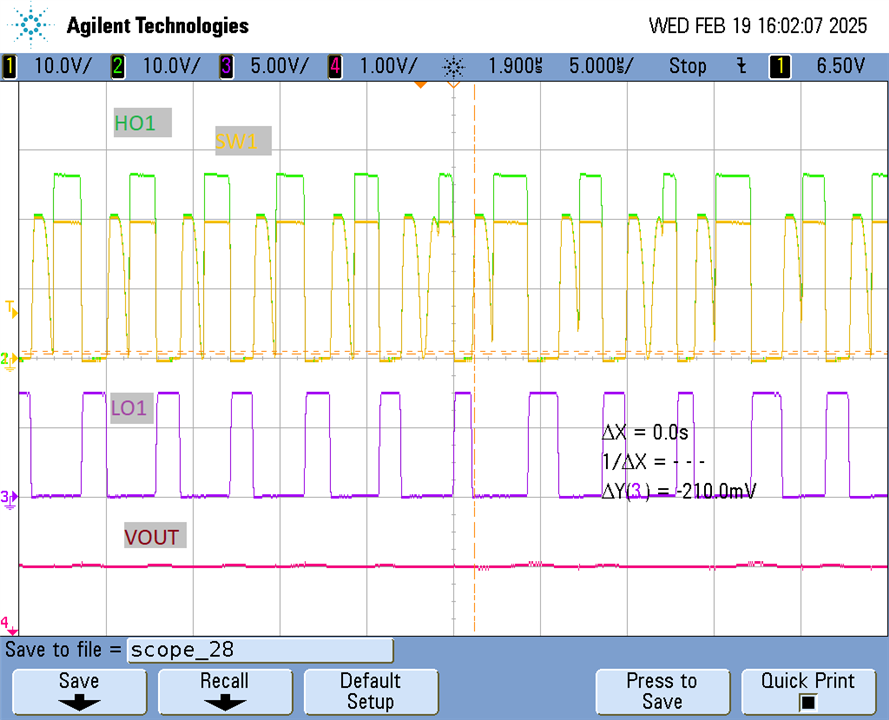

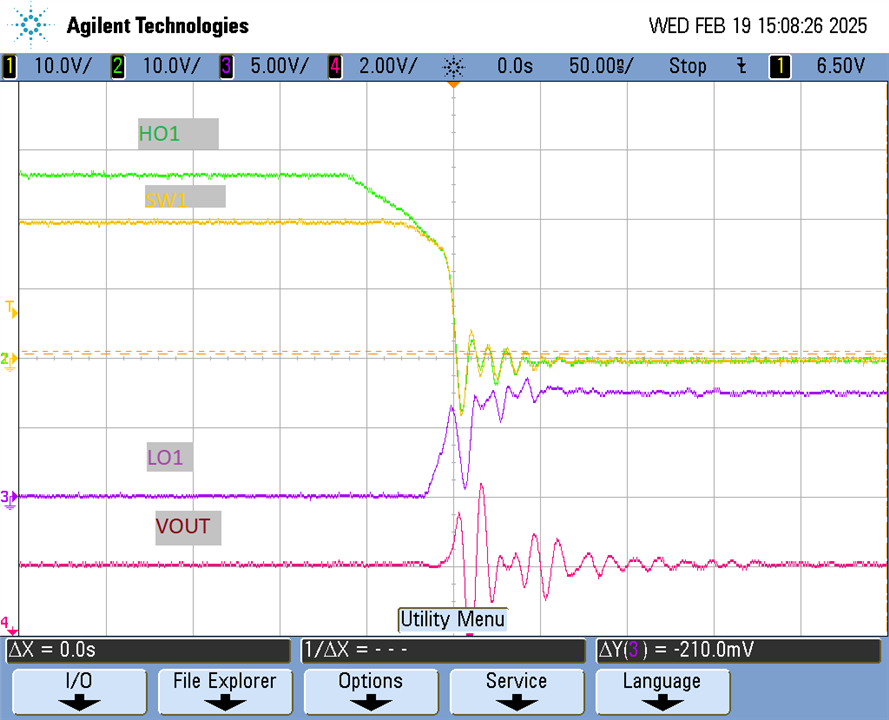

问题在于、控制器似乎定期发生周期跳跃并且(在一个启动模式中)在各个周期之间明显振铃。 这似乎是一个所有开关都断开的时间段。 我们目前没有仪器来观察电感器电流。 我们可以使用焊接到电流感应电阻器上的 Z0探针(950欧姆与同轴电缆连接到50欧姆终端器、200x 探针)。 低侧电流检测波形看起来正常、但可以在高侧开关关断时观察到明显的振铃。 (这 也可能是接地反弹。)