请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM67 工具与软件:

尊敬的专家:

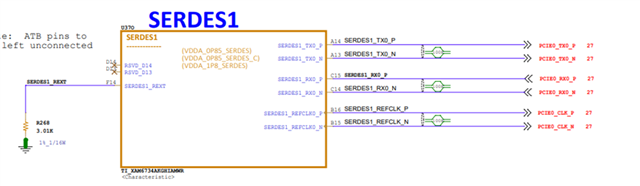

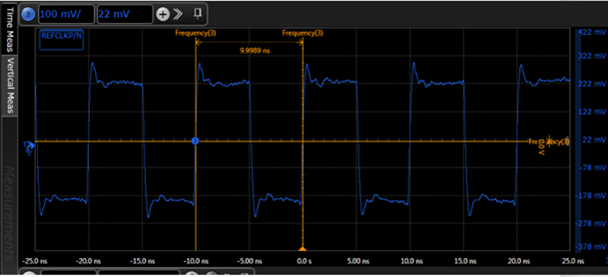

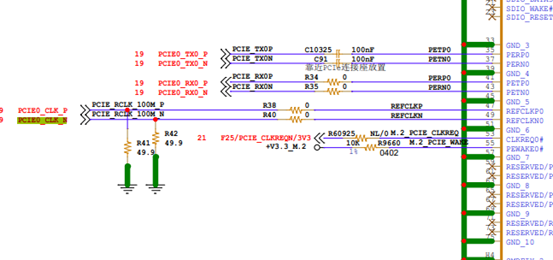

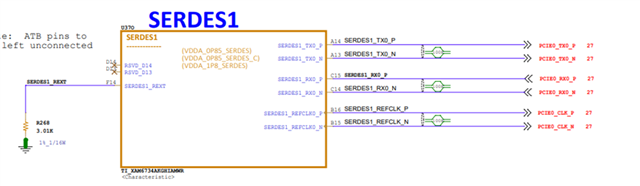

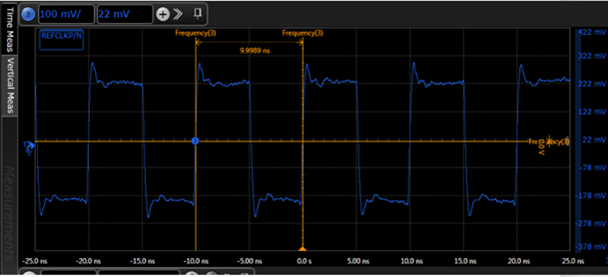

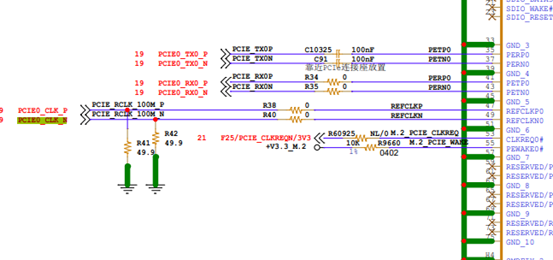

我们的客户使用 PCIE0_CLK_N/P 为 M2提供 CLK。 他们发现波形振幅大约为200mV。 我们想知道我们是否可以修改该振幅?

它们是否需要 PU 50R 电阻? 谢谢

此致、

Zhu Xingyu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的专家:

我们的客户使用 PCIE0_CLK_N/P 为 M2提供 CLK。 他们发现波形振幅大约为200mV。 我们想知道我们是否可以修改该振幅?

它们是否需要 PU 50R 电阻? 谢谢

此致、

Zhu Xingyu

尊敬的 Shreyas:

感谢您的答复。 我们的客户尝试移除50欧姆、发现它确实可以增加振幅。

同样、将基准时钟连接到 EP 也应该具有50欧姆的项。

您能否详细说明一下? 根据我们的理解、SoC 是 RC、M.2 (wifi)是 EP、对吗? SoC 为 EP 提供参考时钟。 那么我们应该在 EP 侧使用50R PU 吗? 谢谢