主题中讨论的其他器件:AM69、、 TUSB321

工具与软件:

根据 AM69 TRM (spruj52)、SERDES 包装器模块能够执行 USB Type-C 通道交换。

但是、根据 AM69 SERDES 文档、 SERDES 0 仅支持一个 USB 3通道(USB3_0):

┌───────────────────┐

| │

PCIE1_LANE0/| │

HYPERLINK_LANE0 │ │ <-> RX0/TX0

──────────────────┤ ├────────────────

│ │

│ │

PCIE1_LANE1/| │

HYPERLINK_LANE1 │ │ <-> RX1/TX1

──────────────────┤ ├────────────────

│ │

│ 4L SERDES │

PCIE3_LANE0/| │

PCIE1_LANE2/│ │

HYPERLINK_LANE2 │ │ <-> RX2/TX2

──────────────────┤ ├────────────────

│ │

│ │

PCIE3_LANE1/| │

PCIE1_LANE3/│ │

USB3_0/│ │

HYPERLINK_LANE3 │ │ <-> RX3/TX3

──────────────────┤ ├────────────────

│ │

└───────────────────┘

这不同于其他处理器。 TDA4VM 文档 SERDES 0 因为具有一个 USB 3通道(USB3_0)、而另一个通道可配置为 USB 3通道交换功能(USB3_0_swap)。

┌───────────────────┐

CPSW0_Q/SGMII_LANE1/│ │

PCIE0_LANE0/│ │

USB3_0_SWAP │ │ <-> RX0/TX0

──────────────────┤ ├────────────────

│ │

│ 2L SERDES │

CPSW0_Q/SGMII_LANE2/│ │

PCIE0_LANE1/│ │

USB3_0 │ │ <-> RX1/TX1

──────────────────┤ ├────────────────

│ │

│ │

└───────────────────┘

我的主要问题是:AM69是否支持 USB 3 Type-C 通道交换? 或者我们是否应该添加多路复用器来选择将哪组超高速信号路由到单个 SERDES 通道?

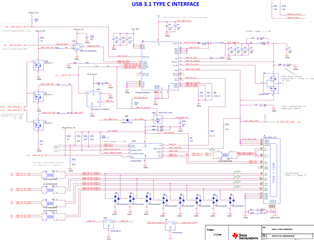

我们当前的 USB 硬件配置基于 SK-AM69评估板的配置、具有以下重要差异:

- USB Type-C 配置为使用 DRD 角色运行。

- 串行器/解串器0通道3:一组来自 Type-C 连接器的 USB_SS_TX/RX 信号

- 串行器/解串器0通道4:来自 Type-C 连接器的另一组 USB_SS_TX/RX 信号

- GPIO0_36:由 TUSB321输出的 USBC_DIR 信号

在对各种器件树更改进行实验之后、PC 和 AM69电路板之间的 USB 3 Type-A 转 Type-C 电缆的行为如下:

- 在一个 Type-C 连接器方向上、PC 能够以 USB 3速度与电路板进行通信。

- Type-C 连接器翻转时、PC 只能以 USB 2速度与电路板通信。

- GPIO0_36会根据 Type-C 连接器的方向而变化。

USB 3 Type-A 转 Type-C 电缆只有一组 SuperSpeed 信号、因此这些信号将连接到 SERDES 0的通道3或通道4、具体取决于电缆的方向。

在器件树中、我们根据 TRM 对 SERDES 通道进行了以下更改。 这里值得注意的一点是 include/dt-bindings/mux/j721E_SERDES0_LANE0_USB3_0_swap 等 ti-serdes.h 定义、但对于 AM69 (J784S4)没有类似的 USB 交换定义。

&serdes_ln_ctrl {

idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>,

- <J784S4_SERDES0_LANE2_PCIE3_LANE0>, <J784S4_SERDES0_LANE3_USB>,

+ <J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>;

};

USB PHY 配置如下所示。

&serdes0 {

status = "okay";

serdes0_usb_link: phy@2 {

reg = <2>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

resets = <&serdes_wiz0 3>, <&serdes_wiz0 4>;

};

};

最后、我们尝试使用 GPIO0_36 作为 USBC_DIR 信号来进行通道交换。

&serdes_wiz0 {

status = "okay";

typec-dir-gpios = <&main_gpio0 36 GPIO_ACTIVE_HIGH>;

typec-dir-debounce-ms = <700>;

};

我在 drivers/phy/ti/phy-j721e-wiz.c (SERDES 包装程序驱动程序)中注意到的一个问题是、它仅支持根据 Type-C 方向 GPIO 位设置 LN10_SWAP 位。 我们尝试修改此值来设置 LN23_swap 位、但在 以 任一方向插入 Type-C 连接器后、未能获得 USB 3速度。

static int wiz_phy_reset_deassert(struct reset_controller_dev *rcdev,

unsigned long id)

{

struct device *dev = rcdev->dev;

struct wiz *wiz = dev_get_drvdata(dev);

int ret;

if (id == 0) {

/* if typec-dir gpio was specified, set LN10 SWAP bit based on that */

if (wiz->gpio_typec_dir) {

if (wiz->typec_dir_delay)

msleep_interruptible(wiz->typec_dir_delay);

if (gpiod_get_value_cansleep(wiz->gpio_typec_dir))

regmap_field_write(wiz->typec_ln10_swap, 1);

else

regmap_field_write(wiz->typec_ln10_swap, 0);

} else {

...

在某些情况下、尝试使用 LN23_swap 位会导致引导期间失败:

[ 6.634286] cdns-torrent-phy 5060000.serdes: Timeout waiting for PHY status ready [ 6.641770] phy phy-5060000.serdes.13: phy poweron failed --> -110 [ 6.647948] cdns-usb3: probe of 6000000.usb failed with error -110