工具与软件:

我有一个有关 AM625SIP 的 PDN 相关问题。 我浏览了大多数在线提供的与硬件相关的文档、非常有信心我们可以处理它们。 我们将使用6层 PCB 并分别紧密地隔开 PWR/GND 层。

我 现在要评估的是以下几点:

实现示例和 PDN 目标 表7-6提到 AM62xx 的每电容最大 L 小于1.5nH、诚然、 这不是 SIP、但没有适用于 SIP 的类似表。

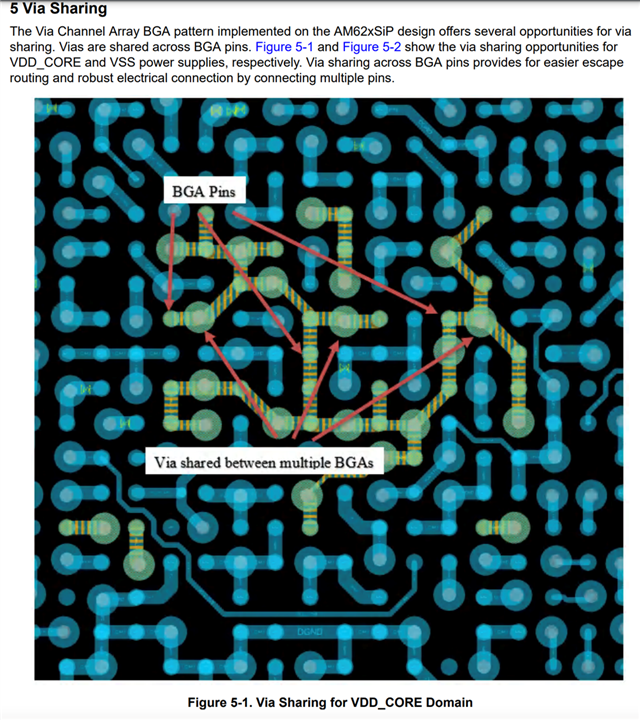

另一个应用手册涉及扇出、 AM62x SiP PCB 设计迂回布线(第5节过孔共享)、展示了如何扇出 VDD_CORE 以及如何在设计时考虑/设计 BGA 的实际占用空间时考虑过孔共享。 但是、图像上显示的迹线(上文应用手册中的快照)已经在迹线本身中添加了>1.2nH、几乎为 PDN (pwr/GND +去耦的夹层)留下了不可能的裕度。

从不同角度看、似乎有两项建议相互矛盾。

您在"过孔共享"方面是否取得了内部成功、或者 PDN 目标是否设置得过于谨慎、或者就 PDN 而言 SIP 变体是否可以更"宽松"?