工具与软件:

尊敬的 SIRs:

我目前正在审查 TDA4VP 的布局设计、并找到了两个与布局相关的设计指南。 但是、我对内容有一些疑问。 能否提供详细的解释? 谢谢你。

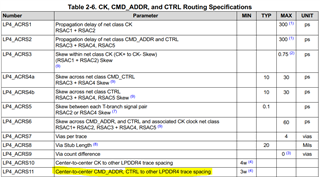

该文档提到 CK、CMD_ADDR 和 CTRL 组拓扑上不应有残桩、但表2-6指出每个迹线的最大过孔数为4。 您能否澄清这一矛盾?

文档规定:"所有测试和探头接入点必须排成一条直线、不得有任何分支或残桩。" 但是、据我所知、大多数高速信号都使用带状线设计、而 LPDDR4 IC 通常采用 BGA 封装设计。 这是否意味着任何 LPDDR4信号都不能有测试点? 由于如果添加测试点、必然会存在分支。

3.在表2-6中、"过孔计数差异"的最大值为0。 这是否意味着仅差分对信号的过孔数量必须相同、或者它是否也适用于 CK、CMD_ADDR 和 CTRL 组拓扑?

4.在表2-6中提到了术语"中心到中心 CMD_ADDR、CTRL 到其他 LPDDR4布线间距"。 在这种情况下、"CTRL"指的是哪些特定信号?

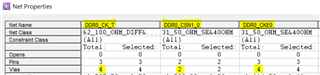

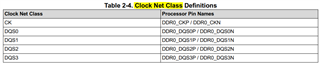

5.表2-7中提到"RSD1中心到中心间距(时钟网类别之间)"一词。 "时钟网类别"中包括哪些特定信号? "RSD1"代表 DQS 信号吗?"RSD2"代表 DQ 和 DM 信号吗?

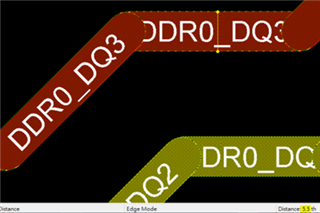

6.在表2-7中,两者的区别是什么 "RSD2中心到中心间距(信号网类别之间)" 和 "RSD2中心到中心间距(信号网类别内)" ?

7.在 Jacinto7 AM6x、TDA4x 和 DRA8x 高速接口设计指南 文件中指出、 "TI 建议过孔残桩短于15mil。" 为什么此要求比前几表中提到的值更严格?

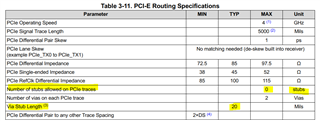

8.为什么表3-7和表3-11规定最大存根数为0、而在文档后面、最小存根长度是定义的?