主题中讨论的其他器件:TMDS64EVM

工具与软件:

我与一位客户合作、试图让他们的 eMMC 在 MMC_HS_52模式(高速52MHz)的 U-Boot 中使用 AM64x。 他们在这个问题上遇到了一些困难。 它们使用的是 Processor-SDK-Linux 9.00.00.03。 我们知道、在9.00.00.03与最新的10.01.10.04 SDK 版本之间、MMC 发生了许多可能很重要但很小的变更。 我们实际上已经分析了其中的一些差异、尤其是 k3-am64-main.dtsi 中的设备树差异。 虽然更新到较新的 SDK 版本可能是个好主意、并且客户有时可能会这样做、但需要采取的措施比目前希望的要多。 如果可能、我们需要在 SDK 版本9.00.00.03上提供近期解决方案。

首先、我们认为我们已经在 am654_sdhci.c 中发现一个关键错误、该错误仍存在于最新的10.01.10.04 SDK 中。 "static const struct timing_data td MMC[]"结构针对 MMC_HS 包含一个带有拼写错误的条目。 我们认为它应该是 ti,itap-del-sel-mms-hs、而不是 ti,itap-del-sel-mcu-hs。 此拼写错误不会影响我们、但它使我们怀疑表中的所有不同模式是否确实都是测试。

我们注意到的第二件事是、"MMC_HS_52模式从" td []"表中完全缺失。 可以通过将其与必要的器件树条目一起添加到表中来支持此模式吗?

在 AM654_sdhci.c 中:

MMC_HS_52 ={"NULL、ti、ITAP-DEL-SEL-MMC-hs52、MMC_CAP (MMC_HS_52)}

在设备树中:

TI、ITAP-DEL-SEL-MMC-Hs52 =<0xA>

我认为省略"OTAP"项会将 OTAPLYEN 设置为0。 请确认。

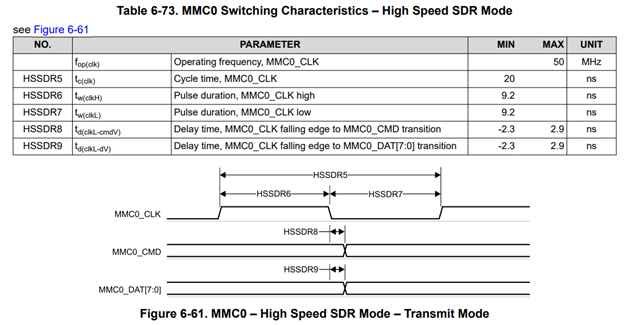

值取自下表:

另一个有点令人困惑的问题是 MMCSD0_HOST_CONTROL1寄存器中的 HIGH_SPEED_ENA 字段的正确值。 在该位清零后、信号时序与下面的图6-61匹配。 如果该位设置为高电平、则数据将在时钟的正边沿开始转换。

以下是 TRM 的摘录:

通过建议将其设置为 MMC_HS_52模式、从而将数据转换移到正时钟边沿、这似乎与数据表中的预期图6-61时序图相矛盾。 在 MMC_HS_52模式下、此位的正确设置是什么? U-boot 似乎遵循 TRM 解释。

如果使用 MMC_HS_52、我认为这符合表6-73 (如果您忽略该52并将其视为50;50 MHz 是示波器上看到的值)、则 u-boot 会设置 HIGH_SPEED_ENA 位。 这会导致上升沿启动并中断时序(至少在数据表建议的 OTAPLYENA = 0时)。

最后、客户似乎确实已使 MMC_DDR_52模式工作。 验证正在进行中。 他们最终可能只是使用 MMC_DDR_52模式。 但是、他们不需要增加带宽、并计划保持 MMC_HS_52模式以增加设计裕度。

谢谢!

Stuart