工具与软件:

您好、TI 专家!

我有 AM6234的开发环境、其中包含我们自己的评估板。

软件 SDK 版本是 SDK-AM62X-08.06.00.42 PROCESSOR-SDK-LINUX-RT。

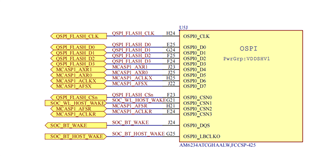

我们的 am6234芯片连接到闪存、型号为 w25q128(页面大小为256字节、擦除大小为4 KiB、总容量为16MiB)、其原理图如下所示:

相应的器件树配置如下:

fss: bus@fc00000 {

compatible = "simple-bus";

reg = <0x00 0x0fc00000 0x00 0x70000>;

#address-cells = <2>;

#size-cells = <2>;

ranges;

ospi0: spi@fc40000 {

compatible = "ti,am654-ospi", "cdns,qspi-nor";

reg = <0x00 0x0fc40000 0x00 0x100>,

<0x05 0x00000000 0x01 0x00000000>;

interrupts = <GIC_SPI 139 IRQ_TYPE_LEVEL_HIGH>;

cdns,fifo-depth = <256>;

cdns,fifo-width = <4>;

cdns,trigger-address = <0x0>;

clocks = <&k3_clks 75 7>;

assigned-clocks = <&k3_clks 75 7>;

assigned-clock-parents = <&k3_clks 75 8>;

assigned-clock-rates = <166666666>;

power-domains = <&k3_pds 75 TI_SCI_PD_EXCLUSIVE>;

#address-cells = <1>;

#size-cells = <0>;

status = "disabled";

};

};

&main_pmx0 {

ospi0_pins_default: ospi0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x000, PIN_OUTPUT, 0) /* (H24) OSPI0_CLK */

AM62X_IOPAD(0x02c, PIN_OUTPUT, 0) /* (F23) OSPI0_CSn0 */

AM62X_IOPAD(0x00c, PIN_INPUT, 0) /* (E25) OSPI0_D0 */

AM62X_IOPAD(0x010, PIN_INPUT, 0) /* (G24) OSPI0_D1 */

AM62X_IOPAD(0x014, PIN_INPUT, 0) /* (F25) OSPI0_D2 */

AM62X_IOPAD(0x018, PIN_INPUT, 0) /* (F24) OSPI0_D3 */

>;

};

};

&ospi0 {

pinctrl-names = "default";

pinctrl-0 = <&ospi0_pins_default>;

spi_nor_flash: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

spi-max-frequency = <25000000>;

cdns,tshsl-ns = <60>;

cdns,tsd2d-ns = <60>;

cdns,tchsh-ns = <60>;

cdns,tslch-ns = <60>;

cdns,read-delay = <4>;

cdns,phy-mode;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "ospi.u-boot";

reg = <0 0x400000>; // 4MB

};

};

};

};

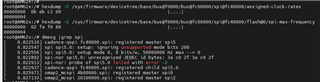

同时、内核的配置如下:

CONFIG_MTD_SPI_NOR=y # CONFIG_MTD_SPI_NOR_USE_4K_SECTORS is not set

我有两个问题:

SPI 最大频率的最大可配置值是多少? 最大速度?是否存在任何限制

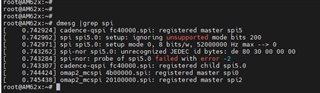

当我将 SPI:频率配置为52000000Hz 时、会出现错误提示 μ s

当我将 SPI 最大频率配置为4166666Hz 时、没有错误:

如何提高 SPI 闪存的写入速度?

当 SPI:频率配置为41666hz 时、将4MB 的数据写入 SPI 闪存需要28.0269秒、如下所示

root@AM62x:~# dmesg |grep spi [ 0.746496] cadence-qspi fc40000.spi: registered master spi5 [ 0.746533] spi spi5.0: setup: ignoring unsupported mode bits 200 [ 0.746542] spi spi5.0: setup mode 0, 8 bits/w, 4166666 Hz max --> 0 [ 0.746860] spi-nor spi5.0: w25q128 (16384 Kbytes) [ 0.746893] 1 fixed-partitions partitions found on MTD device fc40000.spi.0 [ 0.746899] Creating 1 MTD partitions on "fc40000.spi.0": [ 0.746905] 0x000000000000-0x000000400000 : "ospi.u-boot" [ 0.748442] cadence-qspi fc40000.spi: registered child spi5.0 [ 0.749758] omap2_mcspi 4b00000.spi: registered master spi0 [ 0.750860] omap2_mcspi 20100000.spi: registered master spi2 root@AM62x:~# root@AM62x:~# cat /proc/mtd dev: size erasesize name mtd0: 00400000 00010000 "ospi.u-boot" root@AM62x:~# root@AM62x:~# root@AM62x:~# dd if=/dev/urandom of=/dev/mtdblock0 bs=64K count=64 64+0 records in 64+0 records out 4194304 bytes (4.2 MB, 4.0 MiB) copied, 28.1373 s, 149 kB/s root@AM62x:~# dd if=/dev/urandom of=/dev/mtdblock0 bs=1M count=4 4+0 records in 4+0 records out 4194304 bytes (4.2 MB, 4.0 MiB) copied, 28.0269 s, 150 kB/s root@AM62x:~# root@AM62x:~# root@AM62x:~# root@AM62x:~# dd if=/dev/urandom of=test.bin bs=1M count=4 4+0 records in 4+0 records out 4194304 bytes (4.2 MB, 4.0 MiB) copied, 0.0695056 s, 60.3 MB/s root@AM62x:~# root@AM62x:~# dd if=test.bin of=/dev/mtdblock0 bs=1M count=4 4+0 records in 4+0 records out 4194304 bytes (4.2 MB, 4.0 MiB) copied, 28.0232 s, 150 kB/s

当 SPI 最大频率配置为 25000000HZ 时、将4MB 的数据写入 SPI 闪存需要27.1244秒、如下所示:

root@AM62x:~# dd if=/dev/urandom of=/dev/mtdblock0 bs=1M count=4 4+0 records in 4+0 records out 4194304 bytes (4.2 MB, 4.0 MiB) copied, 27.1244 s, 155 kB/s

时钟频率的增加似乎没有影响闪存的写入速度

此致、

Li