工具与软件:

您好、

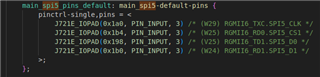

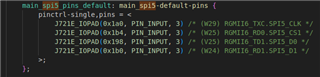

我需要在 Linux 设备树中配置 SPI5。 目前、我使用的配置如下图所示。 我想知道是否仍然需要在路径 pdk_jacinto_10_00_00_27/packages/ti/board/spiki/j721e_evm/j721E_pinmux_data.c 中配置 src 引脚?

此外、我在 SPI5中使用了 CS1、是否应该将参数"reg=<0>"修改为"reg=<1>"? 该参数是什么意思?

此致、

Yang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、

我需要在 Linux 设备树中配置 SPI5。 目前、我使用的配置如下图所示。 我想知道是否仍然需要在路径 pdk_jacinto_10_00_00_27/packages/ti/board/spiki/j721e_evm/j721E_pinmux_data.c 中配置 src 引脚?

此外、我在 SPI5中使用了 CS1、是否应该将参数"reg=<0>"修改为"reg=<1>"? 该参数是什么意思?

此致、

Yang

尊敬的 Yang:

否、无需在 PDK 中配置 SPI5引脚。 如果计划从 Linux 使用 SPI 接口、则只需要在 Linux devicetre 内配置这些图形用户界面、如果计划从 RTOS 使用 SPI 接口、则只需要在 PDK 内配置这些图形用户界面、但不能同时在两者之间配置、以避免资源冲突。

此外、我在 SPI5中使用了 CS1、是否应将参数"reg=<0>"修改为"reg=<1>"?

这是寄存器属性、在本例中表示 spidev 设备位于父总线 main_spi5中的偏移量0处。

如果您尝试了 Linux spidev 示例并发现 SPI 无法正常工作、请随时提出更多问题。 "dmesg"中的完整日志有助于识别当前观察到的情况。

此致、

Takuma

您好!

我想将 GPO0_40导出到/dev/gpiochip0中、但根据上述内容进行配置后、发现没有此节点。 您能告诉我如何配置它吗?

MAIN_spi3_PINS_DEFAULT:main-spi3-default-pins{

PINCTL-SINGLE、PINS =<

J721E_IOPAD (0x144、PIN_INPUT、4)/*(Y25) PRG0_PRU1_GPO17.SPI3_CLK */

J721E_IOPAD (0x11c、PIN_INPUT、4)/*(AA24) PRG0_PRU1_GPO7.SPI3_CS0 */

J721E_IOPAD (0xd4、PIN_INPUT、4)/*(AB26) PRG0_PRU0_GPO9.SPI3_CS1 */

J721E_IOPAD (0xd8、PIN_INPUT、4)/*(AB25) PRG0_PRU0_GPO10.SPI3_CS2 */

J721E_IOPAD (0x124、PIN_INPUT、4)/*(Y24) PRG0_PRU1_GPO9.SPI3_CS3 */

J721E_IOPAD (0x148、PIN_INPUT、4)/*(AA26) PRG0_PRU1_GPO18.SPI3_D0 */

J721E_IOPAD (0x14c、PIN_INPUT、4)/*(AA29) PRG0_PRU1_GPO19.SPI3_D1 */

J721E_IOPAD (0xa4、PIN_INPUT、7)/*(AH22) PRG1_PRU1_GPO19.GPIO0_40 */

>;

};

&main_spi3{

状态="正常";

pinctrl-names ="默认值";

pinctrl-0 =<&MAIN_spi3_PINS_DEFAULT>;

GPIO =<&MAIN_GPIO0 40 GPIO_ACTIVE_HIGH>;

spidev@0{

兼容="ti、spi-evm";

SPI-max-Frequency =<3125000>;

REG =<0>;

spi-cpol =<1>;// CPOL = 1

spi-cpha =<1>;// CPHA = 1

};

spidev@1{

兼容="ti、spi-evm";

SPI-max-Frequency =<3125000>;

reg =<1>;

spi-cpol =<0>;// CPOL = 0

spi-cpha =<1>;// CPHA = 1

};

spidev@2{

兼容="ti、spi-evm";

SPI-max-Frequency =<3125000>;

reg =<2>;

spi-cpol =<0>;// CPOL = 0

spi-cpha =<0>;// CPHA = 0

// interrupts = ;

};

spidev@3{

兼容="ti、spi-evm";

SPI-max-Frequency =<3125000>;

REG =<3>;

spi-cpol =<0>;// CPOL = 0

spi-cpha =<1>;// CPHA = 1

};

};

此致、

Yang

尊敬的 Yang:

我有点困惑、该线程的问题和目标是什么。 您能否说明问题是:

最新的问题是关于 GPIO、因此我假设目标是设置一个 通用 GPIO 以进行手动切换。 如果是、则 sysfs 部分会过时、因为 sysfs 已替换为 chardev、但此常见问题解答中包含了有关 devicetre 的一些说明: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/918654/faq-tda4vm-dra829-am65xx-linux-configuring-gpios

有关新 chardev 和 GPIO 工具的更多信息、请参阅此常见问题解答: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1260373/faq-transitioning-the-gpio-userspace-interface-from-sysfs-to-chardev

此致、

Takuma