工具与软件:

icssg dirver:从 sdk9.0中的 uboot 移植

测试方法:PHY 内部环回

编译链:GCC

在测试原始数据时、每1ms 发送1024个字节的数据、接收数据、然后检查接收长度、有时可以是1532。

读取 MII_G 模块的统计寄存器来显示接收到的总数据长度可以除以每个数据包的长度、也就是说、MII_G 模块接收到的数据的长度没有问题。

PRU 模块接收数据后再将数据传输到 DMA 存在问题。

这一问题的原因是什么以及我如何解决它。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

icssg dirver:从 sdk9.0中的 uboot 移植

测试方法:PHY 内部环回

编译链:GCC

在测试原始数据时、每1ms 发送1024个字节的数据、接收数据、然后检查接收长度、有时可以是1532。

读取 MII_G 模块的统计寄存器来显示接收到的总数据长度可以除以每个数据包的长度、也就是说、MII_G 模块接收到的数据的长度没有问题。

PRU 模块接收数据后再将数据传输到 DMA 存在问题。

这一问题的原因是什么以及我如何解决它。

尊敬的 Expert:

更多问题描述供您参考、

1)环回发送数据包长度(如果固定)为1024字节、发送频率为每秒一次

2)发生问题时,接收描述符中的接收数据包长度显示它是1532 ,多余的508字节(1532-1024)是"0"

3) MAC 统计模块显示外部接收数据包长度是根据上述票证中提到的计算正确的。

@张鹏东,按照所说,请上传描述符字段信息和更多相关的日志作为参考。

-Thomas

PHY 内部环发送1024个字节、周期为1ms。

MII_G 统计信息读取指示每次发送的数据为1064字节

MII_G 接收的数据为1056个字节。

接收线程绑定到 CPU 0、 CPU 使用量高。无法及时接收数据。

我们将描述符的长度设置为2048、没有覆盖情况

这是日志之一

RX_GOOD_FRAMES = 34758

RX_BROADCAST_FRAMES = 34760

RX_MULTICAST_FRAMES = 34767

RX_CRC_ERROR_FRAMES = 0

RX_MII_ERROR_FRAMES = 0

RX_ODD_NIBABLE_FRAMES = 0

RX_FRAME_MAX_SIZE = 2000

RX_max_size_error_FRAMES = 0

RX_FRAME_MIN_SIZE = 64

RX_MIN_SIZE_ERROR_FRAMES = 0

RX_OVERRUNRY_FRAMES = 0

RX_class0_hits = 34824

RX_CLASS1_HASKS = 0

RX_CLASS2_Hits = 0

RX_CLASS3_Hits = 0

RX_CLASS4_Hits = 0

RX_CLASS5_Hits = 0

RX_class6_hits = 0

RX_class7_hits = 0

RX_class8_hits = 34850

RX_class9_hits = 34857

RX_class10_hits = 0

RX_class11_hits = 0

RX_class12_hits = 0

RX_class13_hits = 0

RX_class14_hits = 0

RX_class15_hits = 0

RX_SMD_FRags = 0

RX_BUCKET1_SIZE = 64

RX_BUCKET2_SIZE = 128

Rx_Bucket3_SIZE = 256

Rx_Bucket4_SIZE = 512

RX_64B_FRAMES = 0

RX_BUCKET1_FRAMES = 0

RX_BUCKET2_FRAMES = 0

RX_BUCKET3_FRAMES = 0

RX_BUCKET4_FRAMES = 0

RX_BUCKET5_FRAMES = 34886

RX_TOTAL_BYTES = 36839616

RX_TX_TOTAL_BYTES = 73958320

TX_GOOD_FRAMES = 34886

TX_BROADCAST_FRAMES = 34886

TX_MULTICAST_FRAMES = 34886

tx_odd_nibble_frames = 0

TX_UNDERFLOW_ERRORS = 0

tx_FRAME_max_size = 2000

tx_max_size_error_FRAMES = 0

TX_FRAME_MIN_SIZE = 64

TX_MIN_SIZE_ERROR_FRAMES = 0

TX_BUCKET1_SIZE = 64

TX_BUCKET2_SIZE = 128

tx_bucket3_size = 256

tx_bucket4_size = 512

TX_64B_FRAMES = 0

TX_BUCKET1_FRAMES = 0

TX_BUCKET2_FRAMES = 0

TX_BUCKET3_FRAMES = 0

TX_BUCKET4_FRAMES = 0

TX_BUCKET5_FRAMES = 34886

tx_total_bytes = 37118704

____________________________________

从上面的日期、wo 可以得到

tx_total_bytes = 37118704

37118704/1064 = 34,886

TX_GOOD_FRAMES = 34886

TX_BUCKET5_FRAMES = 34886

从上面的数据可以看出、计算所得的发送包总数等于统计值、发送没有问题

RX_TOTAL_BYTES = 36839616

36839616/1056 = 34866

RX_BUCKET5_FRAMES = 34886

RX_GOOD_FRAMES = 34758

问题似乎是接待。

我读取描述符字段数据、接收长度也是 1536 (包括 CRC 4个字节)。

然后、我们将绑定到接收线程的 CPU。 此内核仅发送和接收网络端口的任务。

在当前测试中、当速度为70MB/s 时、不会丢失数据包、也不会出现异常长度

问题是、如果 CPU 负载过大、为什么长度异常

不幸的是、在70MB/s 的长时间测试中(48小时)(接收和发送线程都绑定到内核1、内核1只有这两个线程)、长度再次延长。

我们的硬件板具有 icssg 端口和 cpsw 端口、它们都使用 udma 和 ringacc。

在随后的 cpsw 网络端口测试中、问题的长度也会出现。

发送数据的长度是1024、周期是1ms、接收线程绑定到内核0、内核0 CPU 负载很重、接收网络数据时可以达到100%。

出现问题时、接收长度变为1536、描述符中的长度数据也是1536。 测试 ringacc 的驱动程序后、未发现代码问题。

基于上述,我觉得问题可能是在 pis-l->dma 的过程。

我正在测试 icssg eth 的驱动程序,我怎么能找到问题。

您好 JC

根据和鹏东的沟通、我得到了如下反馈:

1)在 CPU 负载较高的情况下,如以下2种情况,内核1同时运行接收和发送任务,或内核0仅运行接收,但内核0在高负载下,将出现异常长度问题。

2)如果 CPU 负载较低,挂起没有测试这种情况,因此很难判断该问题是否由高 CPU 负载引起,我认为您最后的回复尝试使 PRU_ICSSG 运行,因为333MHz 基于该问题是 由高 CPU 负载引起的。

@张鹏东,如果有任何新的测试完成,请澄清并更新。

3)因为这个问题不仅是相关的 PRU_ICSSG,而且也发生在 CPSW,所以 Pisl- DMA 路径可能有一些问题,我给 pengdong,但仍然想从 BU 专家的建议得到更多的指导,谢谢!

-Thomas

这是 cpsw 网络端口驱动程序测试性能的记录。

板 A 的发送线程绑定内核1、板 B 的接收线程绑定内核1。

两个电路板的内核1中没有其他任务、并且在长期测试中仍然存在长度异常。

当在 uDMA_receive 中检测到 pkt_len (如1536)时、描述符信息将按上图所示打印。

日志显示描述符中的长度为1536 (0x600)。

在此例中、cpsw 接收端口号是0、通常为1或2。

当在 uDMA_receive 中检测到 pkt_len (如1536)时、描述符信息将按上图所示打印。

日志显示描述符中的长度为1536 (0x600)。

在此例中、cpsw 接收端口号是0、通常为1或2。

[报价]您可以在此处查看1536字节长度的数据包内容吗? 是填充的测试数据包(长度为1024字节)或其他一些数据包...

假设上述情况意味着大多数帧都正常、只是偶尔为0x600长度。 比例是多少、长度不正确的帧的频率是多少。 您能否在这个0x600长度的情况下捕获整个帧? 以太网 CRC 是否仍然正确? TCP 或 UDP 校验和是否正确?

我将重点介绍 CPSW 案例、仅删除一个变量(固件版本、通常为 ICSSG)。 CPSW 的错误是否相同、长度为0x600字节、最后508个字节为0 (CRC 正确)?

[quote userid="642553" url="~/support/processors-group/processors/f/processors-forum/1474941/am6442-icssg1-eth-port-receive-length-is-increased-1532测试方法:phy 内部环回PHY 使用什么?

Pekka

还有一件事需要检查。 以太网帧长度位置中的0x600表示 Ethertype 不是长度。 https://networkengineering.stackexchange.com/questions/51467/ethernets-frame-format-length-or-ethertype 和 https://www.iana.org/assignments/ieee-802-numbers/ieee-802-numbers.xhtml 。 这可能是巧合、但恰好是0x600长度、因为在双重用途字段中出现错误偶尔似乎过于巧合。 之前的注释仍然存在、对 CPSW 重复、但请使用以太网标头捕获整个帧。

Pekka

它是填充数据包。 软件包中的内容是正确的、但末尾有额外的0

cppi5_hdesc_get_pktlen ()返回1536。

以下是前一个测试数据的尾部:

b7 b8 b9 ba bb bc bd be bf c0 c1 c2 c3 c4 c5 c6

C7 C8 C9 cb cc cd ce cf d0 d0 d1 d2 d3 d4 d5 d6

D7 D8 D9 da db 直流 DD Df e0 E1 E2 E4 E5 E6

e7 e8 e9 eB eB ee ef f0 f1 76 C9 EC 4D 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0

测试方法:PHY 内部环回

PHY 使用什么?

[报价]您能回答这个问题吗? 在任何其他以太网测试中是否看到0x600长度字段?

什么是比率、长度不正确的帧有多频繁。 您能否在这个0x600长度的情况下捕获整个帧? 以太网 CRC 是否仍然正确? TCP 或 UDP 校验和是否正确?[/QUOT]尤其是这个比率、您多久看到这些0x600长度用零框架填充一次?

Pekka

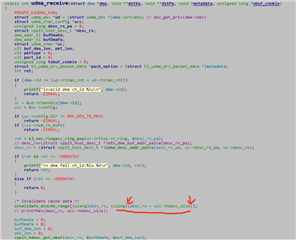

上图显示了正常通信。期间 udma_receive 中打印的描述符的内容

/**

*描述符标头,存在于所有类型的描述符中

*/

结构 cppi5_desc_hdr_t

{

u32 pkt_info0;/*数据包信息字0 (缓冲区描述中的 N/A)*/

u32 pkt_info1;/*数据包信息字1 (缓冲区说明中不适用)*/

u32 pkt_info2;/*数据包信息字2缓冲区回收信息*/

U32 src_dst_tag;/*数据包信息字3 (缓冲区描述中不适用)*/

}__packed;

Pkt_Info1、 pkt_info2、src_dst_tag 不是0。

当接收长度异常时、这些值为0。

下面是测试数据。

recv-0 len 1532.

FF ff ff ff ff ff ff ff ff ff ff ff FF 2b 2c 2d 2e 2f 30 aa 99 33 34 35.

36 37 38 39 3a 3b 3c 3D 3e 3f 40 41 42 43 44 45

[报价]这一切都来自您自己的驱动程序代码、因此让我们尝试确认您正在打印的内容。 假设上述情况是以太网帧的起始? 如果这看起来不正确、请进行更正:

目的 MAC 地址为0xFF FF FF FF FF FF FF FF、这是广播

源 MAC 为0x2B 2C 2D 2E 2F 30、看起来像是一个预填充模式、不会使用实际 MAC 地址进行覆盖

EtherType/Length 字段为0x AA 99、这是您有意使用的某个以太网类型吗?

这是否符合您的预期?

PHY 为 YT8531

其他测试也有异常长度

这种现象的出现是不确定的,有时是几分钟,有时是几个小时

[报价]是否有此 PHY 的数据表? 我可以找到 https://www.motor-comm.com/Public/Uploads/uploadfile/files/20240513/YT8531C-CA_YT8531H-CA_YT8531DC-CA_YT8531DH-CA_YT8531P-CAProductBrief_v0.1.pdf 、但产品说明书似乎不可用?

为了排除任何硬件或 PHY 问题、您可以在 TI EVM 上运行相同的测试吗?

长度异常、因此并非总是0x600?

您是否尝试过 PHY 示例包以外的内容、您是否也观察到长度为0x600 (或其他内容已损坏)?

Unknown 说:]测试方法:phy internal loopback

未使用环回

最初发布的问题是使用电机通信 YT8531 PHY 的 PHY 环回功能的环回。 它显然具有环回功能(但没有适用于 PHY 的数据表)。 但现在您转向尝试2块电路板。 这是一个很好的数据点。

而不是直接说明、但似乎您在 A53上使用自己的 RTOS。 对于高速缓存一致性和设置、描述符和缓冲区所在的 MMU 页表设置是什么? 其他可能有趣或相关的设置、您能否共享您正在使用的编译器标志和编译器版本?

您可以在 TI EVM 上运行该 RTOS 吗? 您是否看到以太网帧存在同样的问题? 或者、您是否可以在电路板上运行 TI MCU+、以查看经测试的 TI 驱动程序是否也存在问题(TI SDK 不直接支持 PHY)。

Pekka

可以、有两种类型的测试:一种电路板执行环回测试、另一种电路板连接执行性能测试。

这两项测试都有此问题。

一个月前采用了 PHY 环路测试、一周前采用了两个电路板连接测试。

现在有三个测试:

1.在环回测试中、实验板接收绑定内核1、发送绑定内核1、发送124个数据包(每包1488字节)、延迟1ms。 数据包根据1 GB/s 的带宽发送

2.

电路板发送、发送线程绑定内核1、发送124个数据包、每个数据包1488字节、延迟1ms 根据1Gb/s 的带宽发送

B 板接收、接收线程绑定 内核1、并在接收后检查数据包序列号和长度

3.回送测试是使用 Tronlong 的开发板(与 TI EVM 相同)执行的。

这三项测试都存在长度异常的问题

稍后、我将添加 MMU 和高速缓存。的设置

在 uDMA_receive()中、

unvalidate_dcache_range (((ulong) desc_rx、(ulong)(desc_rx + ucc->hdesc_size));

这有什么问题吗?

代码中括号的范围是错误的?

它应该为 unvalidate_dcache_range ((ulong) desc_rx、(ulong)(desc_rx)+ ucc->hdesc_size);

unvalidate_dcache_range (((ulong) desc_rx、(ulong)(desc_rx + ucc->hdesc_size));

--> 失效缓存范围((ulong)desc_rx,(ulong)(desc_rx )+UCC->hdesc_size) ;

我根据上面的帖子修改了代码,测试了12小时,没有出现问题。 如果不进行修改、肯定会进行4-5小时的测试。

问题迎刃而解。

谢谢大家!

如果您随机刷新与您打算执行的操作无关的区域的缓存、精确的内存设置(MMU 页表)和其他缓存方式可能会导致异常行为。 我建议您严格遵守 MMU 设置和所运行软件的权限。

如果您的驱动程序在 EL1异常级别中运行、则尤其如此。

对于软件高速缓存管理的一般压力测试、我建议并行运行一个数千兆字节 memcpy()作为高速缓存跟踪器、例如、而不是空闲来发现竞争条件。

Pekka