工具与软件:

是否可以在没有额外100MHz 外部参考时钟源的情况下使用 SoC 的 SGMII 接口、以便 SoC 的唯一时钟输入将是 WKUP_OSC0处的振荡器?

在 SoC 原理图符号的 EVM 设计(PROC141E5)中、PCIe_REFCLK0和 PCIe_REFCLK2输出都与 SERDES1块相关联。

我可以将 PCIe_REFCLK2输出用作 SERDES2的时钟 SGMII5和-7接口吗?

任何 PCIe_REFCLKx 输出是否可以与任何 SERDESx 关联?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

是否可以在没有额外100MHz 外部参考时钟源的情况下使用 SoC 的 SGMII 接口、以便 SoC 的唯一时钟输入将是 WKUP_OSC0处的振荡器?

在 SoC 原理图符号的 EVM 设计(PROC141E5)中、PCIe_REFCLK0和 PCIe_REFCLK2输出都与 SERDES1块相关联。

我可以将 PCIe_REFCLK2输出用作 SERDES2的时钟 SGMII5和-7接口吗?

任何 PCIe_REFCLKx 输出是否可以与任何 SERDESx 关联?

您好!

[报价 userid="640895" url="~/support/processors-group/processors/f/processors-forum/1485757/tda4vh-q1-using-sgmii5-and--7-from-serdes2-without-additional-100mhz-external-reference-clock-source "]是否可以使用 SoC 的 SGMII 接口而无需额外的100MHz 外部参考时钟源、以便 SoC 的唯一时钟输入将是 WKUP_OSC0处的振荡器?是的、可使用来自 PLL 的内部时钟。

MAIN_PLL2_HSDIV4默认为100MHz、可以选择作为串行器/解串器基准时钟的父时钟。

不需要、您可以自行使用内部时钟。

此致、

Sudheer

您好!

[报价 userid="640895" url="~/support/processors-group/processors/f/processors-forum/1485757/tda4vh-q1-using-sgmii5-and--7-from-serdes2-without-additional-100mhz-external-reference-clock-source/5708500 #5708500"]但是我是否还需要 SGMII 时钟信号用于在 SoC 与我要通信的设备之间进行通信?使用 MAC 还是 PHY 作为对等器件来与 TDA4的 MAC 进行通信。

如果器件(MAC/PHY)支持内部时钟、您可以使用它们、如果不支持、则需要使用外部时钟。

TDA4可以生成内部时钟并用于串行器/解串器。

SGMII 接口时钟的时钟为100MHz。

您可以使用 SOC 输出时钟来驱动外部器件。

但是、在 TI EVM 上、我们为 QSGMII PHY 使用外部时钟源。 请参阅 EVM 原理图以供参考。

https://www.ti.com/tool/J784S4XEVM

此致、

Sudheer

谢谢、我认为这解决了我现在的部分问题、

但我仍然想了解的是、SoC 的哪些 REFCLK 输出可与 SERDES2结合使用 如果 使用 SoC 输出时钟驱动外部器件?

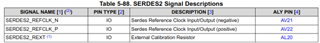

在 技术参考手册(SPRUJ52)图12-125中、PCIe_REFCLK 显示为时钟输出、SERDES_REFCLK 显示为输入、但在规格(SPRSP79B)中、表5-88 SERDES_REFCLK 定义为 IO。

SERDES_REFCLK 是否也可以输出参考时钟、或者 PCIe_REFCLK 是否应始终用于此目的?

TRM 和规范不专门强调哪些 REFCLK 可与哪些 SERDES 模块配合使用。 我可以将任何 REFCLK 与 SERDES2结合使用吗、也可以仅使用例如 PCIe_REFCLK 吗 2. 和 SERDES_REFCLK 2. 稳定性视频 2. ?

您好!

可以将 SERDES_REFCLK 用于外部器件的 SGMII。

但是、当用于 PCIe 接口时、需要使用 PCIe_REFCLK。

Shreyas Rao

您能否确认相同事项。

此致、

Sudheer