Thread 中讨论的其他器件:SK-AM62-LP

工具与软件:

您好、亲爱的专家

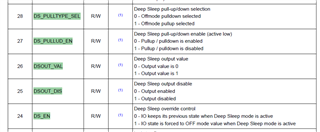

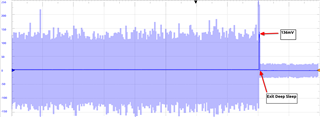

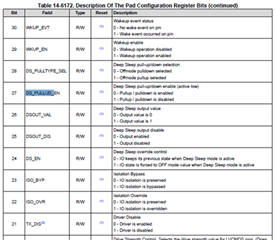

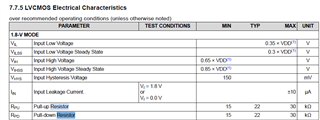

如标题说明、客户希望在 SoC 切换为 "深度睡眠"或"部分 I/O "模式后保持"最后一个 I/O 状态"。

例如、GPIO0_49 =低电平处于"正常工作模式"、然后我们希望 GPIO0_49"保持低电平" (当 SoC 切换为"深度睡眠"或"部分 I/O"模式时)。

有可能吗?

或者、我们是否可以在 SOC (AM62)交换到"深度睡眠"或"部分 I/O "模式时设置每个 GPIO 状态?

非常感谢

Gibbs