工具与软件:

尊敬的社区专家:

我有一些关于 SERDES_REFCLK 方向的问题:

-例如当 SOC 引导模式设置为 PCIe 时,我可以想象 方向是内部强制输入。 这是正确的吗? 我还想强制进入 EP 模式。 这是正确的吗?

-在其他引导模式中,我想象方向和模式(RC vs EP )都可以由软件独立选择。 这是正确的吗?

此致、

Bruno

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的社区专家:

我有一些关于 SERDES_REFCLK 方向的问题:

-例如当 SOC 引导模式设置为 PCIe 时,我可以想象 方向是内部强制输入。 这是正确的吗? 我还想强制进入 EP 模式。 这是正确的吗?

-在其他引导模式中,我想象方向和模式(RC vs EP )都可以由软件独立选择。 这是正确的吗?

此致、

Bruno

Bruno、您好!

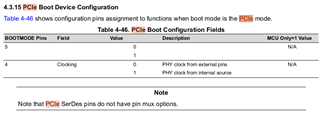

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1487671/tda4vh-q1-serdes_refclk-direction ]]-例如、当 SOC 引导模式设置为 PCIe 时、我可以想象 在内部强制输入方向。 这是正确的吗? 我还想强制进入 EP 模式。 这是正确的吗?PCIe 将采用 EP、SERDES_REFCLK 方向(也就是说、是否使用外部参考时钟还是内部参考时钟)也将由引导模式引脚决定、您可以将其拉高或拉低。

-在其他引导模式中,我想象方向和模式(RC vs EP )都可以由软件独立选择。 这是正确的吗?

[报价]不确定我是否正确理解了这个问题、但是在我们的 Linux 内核驱动程序中、使用内部还是外部参考时钟以及是设置为 RC 还是 EP 都可以在软件中配置。 相比之下、ROM 代码受限。

此致、

Takuma

你好、Takuma、

感谢您的回答。

我不能肯定地理解自己。

您所指的表4-46附带了"时钟"字段、允许 在内部和外部之间进行选择。

当然、选择"external"需要将时钟引脚作为输入。

但恰恰相反、对于我来说、选择"内部"意味着引脚成为输出是不明显的。 是这样吗? 在这种情况下、它可以保持输入状态、也可以更改为输出、而不会影响 PCIe 行为。 (我错了吗?)

(我担心电路板上会有一个时钟驱动器来为时钟引脚供电、我想知道是否存在 SOC 和驱动器都将发生电气冲突的情况、因为它们都是同一个网络的来源。)

此致、

Bruno

Bruno、您好!

到目前为止、我们仅验证了 ROM 代码、 在 TI J784S4 EVM 的 J17连接器上将 PCIe 引导模式设置为内部时钟。 SDK 不支持 PCIe 引导、因此许多功能未经验证。 外部时钟是这些特性之一。

但是、为了提供一些可能有帮助的原理图信息、 J17连接到 PCIe_REFCLK0_OUT_P/N:

在 Linux 内核中、我们将 PCIe 设置为使用 SoC 内部时钟来提供 PCIe 连接器参考时钟。

另一方面、还有第二个 PCIe 插槽 J14连接器、该连接器将参考时钟从外部时钟提供给 SoC 和 PCIe 连接器。 为此、 使用 R_SOC_SERDES1_REFCLK_P/N:

Linux 内核会相应地进行此设置。

由于参考时钟的输入和输出通过不同的路径、因此我认为不存在问题。 但是、如果参考时钟存在硬件问题、请随时打开新的 E2E 票证、我们可以邀请硬件工程师来查看。

此致、

Takuma