主题中讨论的其他器件:SysConfig

工具与软件:

我们有新的设计请求两个 MCSPI 端口、如何为每个 MCSPI 端口配置 uDMA、我知道如何将 uDMA 配置为一个 MCSPI 端口。 下面是用于配置一个 MCSPI 端口的代码、 udma_init ()似乎可以调用一次、但如何为第二个 SPI 再创建一个 uDMA?

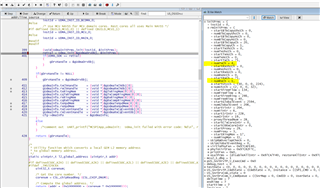

Udma_Drv 54 MCSPIApp_udmaInit (SPI_v1_HWAttrs *cfg)

{

int32_t retVal = uDMA_SOK;

Udma_Init 4.30ms initPrms;

uint32_t instId;

if (gDrvHandle == NULL)/* PRQA S 2,991,2994 */

{

/* uDMA 驱动程序初始化*/

#if 已定义(SOC_AM64X)

/*对 AM64x 使用块复制 DMA 实例*/

instId = UDMA_INST_ID_BCDMA_0;

#else

/*将 MCU NAVSS 用于 MCU 域内核。 REST 内核全部使用主 NAVSS */

#if 已定义(BUILD_MCU1_0)||已定义(BUILD_MCU1_1)

instId = UDMA_INST_ID_MCU_0;

#else

instId = UDMA_INST_ID_MAIN_0;

#endif

#endif

(void) UdmaInitPrms_init (instId、&initPrms);

retval = udma_init (&gUdmaDrvObj、&initPrms);

if (uDMA_SOK == retVal)

{

gDrvHandle =&gUdmaDrvObj;

}

}

if (gDrvHandle!= NULL)

{

gDrvHandle =&gUdmaDrvObj;

gUdmaInfo.txChHandle =(void *)&gUdmaTxChObj;

gUdmaInfo.rxChHandle =(void *)&gUdmaRxChObj;

gUdmaInfo.txRingMem =(void *)&gTxRingMem[0];

gUdmaInfo.cqTxRingMem =(void *)&gTxCompRingMem[0];

gUdmaInfo.rxRingMem =(void *)&gRxRingMem[0];

gUdmaInfo.cqRxRingMem =(void *)&gRxCompRingMem[0];

gUdmaInfo.txHpdMem =(void *)&gUdmaTxHpdMem[0];

gUdmaInfo.rxHpdMem =(void *)&gUdmaRxHpdMem[0];

gUdmaInfo.txEventHandle =(void *)&gUdmaTxCqEventObj;

gUdmaInfo.rxEventHandle =(void *)&gUdmaRxCqEventObj;

cfg->dmaInfo =.gUdmaInfo;

}

设计

{

/* uart_printf ("MCSPIApp_udmaInit:udma_init 失败、出现错误代码:%d\n"、retVal);*/

}

返回(gDrvHandle);

}

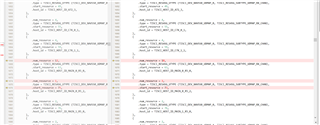

SPI_HWAttrs SPI_cfg =

{

.baseAddr = CSL_MCSPI0_CFG_BASE、

.intNum = CSLR_MAIN2MCU_LVL_INTR0_IN_MCSPI0_INTR_SPI_0

.pinMode =(uint32_t) SPI_PINMODE_4_PIN

.chNum = MCSPI_CHANNEL_0、

//.chMode = MCSPI_SINGLE_CH、

.chMode = MCSPI_MULTI_CH、

enableIntr =(bool) me_false、

.inputClkFreq = 48000000U、

.initDelay = MCSPI_INITDLY_0、

.rxTrigLevel = MCSPI_RX_TX_FIFO_SIZE、

.txTrigLevel = MCSPI_RX_TX_FIFO_SIZE、

.chnCfg =

{

[0]=

{

.csPolarity = MCSPI_CS_POL_LOW、

.dataLineCommMode = MCSPI_DATA_LINE_COMM_MODE_7、

.tcs = MCSPI_CH0CONF_TCS0_ZEROCYCLEDLY、

.trMode = MCSPI_TX_RX_MODE

}、

[1]=

{

.csPolarity = MCSPI_CS_POL_LOW、

.dataLineCommMode = MCSPI_DATA_LINE_COMM_MODE_7、

.tcs = MCSPI_CH1CONF_TCS1_ZEROCYCLEDLY、

.trMode = MCSPI_TX_RX_MODE

}、

}、

.rxDmaEventNumber = CSL_PDMA_CH_MAIN_MCSPI0_CH0_RX、

.txDmaEventNumber = CSL_PDMA_CH_MAIN_MCSPI0_CH0_TX、

};

spi_cfg.edmaHandle =(void *) MCSPIApp_udmaInit (&SPI_cfg);

spi_cfg.dmaMode =(bool) true;